Dall'inizio di aprile l'utente Underfox ha condiviso con un lungo thread su Twitter vari schemi di brevetti AMD, compresi aggiornamenti riguardanti futuri processori e GPU, facendo inoltre ben intuire come l'azienda sia sempre intenzionata a realizzare ciò che si prefisse anni fa: realizzare l'EHP.

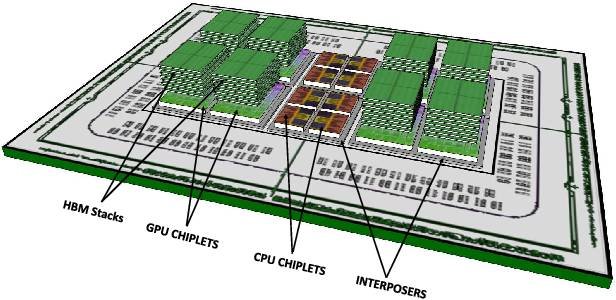

EHP, Exaescale Heterogeneous Processor, è un ambizioso e avveniristico progetto di AMD datato 2015. La casa di Sunnyvale decise di realizzare un processore, o meglio, un package in cui potevano trovare posto 32 core Zen, una GPU con architettura Greenland (GCN5 - Graphics Core Next 5) e memoria HBM2. Il progetto era però impossibile da realizzare all'epoca, anche per il fatto che né Zen né Greenland esistevano.

Nel corso del 2017 abbiamo però visto concretizzarsi sul mercato l'architettura Zen con i primi processori Ryzen e l'architettura grafica GCN5 con le schede video della serie AMD RX Vega con memorie HBM2. Nello stesso anno AMD parlò non di come e quando avrebbe realizzato l'EHP, ma dove l'avrebbe implementato: così definì un ecosistema ENA, Exascale Node Architecture, in cui usando 100000 nodi EHP si sarebbe raggiunta e gestita una potenza pari a 1,6 exaflops per calcoli FP64 (doppia precisione in virgola mobile). Definì anche l'organizzazione interna del package EHP, parlando di chiplet, cioè di 8 gruppi da 4 core Zen ciascuno per il processore centrale e di 8 gruppi da 32 CU (Compute Unit) GCN5 per il processore grafico.

After a very long wait and all the problems I am going through because of COVID-19, I was finally able to format a new list of recently published patents from AMD... I hope you enjoy!

— Underfox (@Underfox3) April 2, 2020

Follow the thread! pic.twitter.com/8uLYegwBZ1

Sappiamo che in tre anni AMD é riuscita ad utilizzare la suddivisione in chiplet nei suoi processori, aumentando le rese produttive e conseguentemente abbassando i costi di produzione, realizzando chip con 64 core su singolo package, vedi Epyc "Rome" (seconda generazione) e Ryzen Threadripper 3990X.

Apprendiamo inoltre, dall'ultimo Financial Analyst Day tenuto il 5 marzo scorso, che AMD implementerà in futuro il die stacking X3D, per inserire nel package chip e diversi elementi collegati insieme sia sul piano orizzontale che in verticale, un pò come avviene nelle HBM, ma con qualche evoluzione in più. Nella stessa sede AMD ha spiegato come le future tecnologie dialogheranno tra loro, evolvendo l'attuale Infinity Fabric in Infinity Architecture.

Sembra proprio che AMD stia realizzando e conquistando quelle tecnologie che le permetteranno di realizzare finalmente questo EHP.

L'utilizzo che poi si andrà a fare di una architettura altamente performante ed efficiente nei calcoli eterogenei è presto detto: datacenter e intelligenza artificiale, semplificando banalmente. Tutti quei scenari d'utilizzo dove non conta solo la potenza di calcolo, ma anche annullare se e dove possibile le varie latenze dovute allo scambio dati tra i vari elementi computazionali: si evince subito il beneficio a tal proposito che ne avrebbe il processore a comunicare con la GPU se fosse tutto sullo stesso package.

Stai cercando un processore a 8 core? Valuta questo AMD Ryzen 7 3700X in promozione!