Cadence ha annunciato di aver eseguito con successo il tape out dei blocchi di base della propria memoria GDDR6 (anche detti GDDR6 IP) con processo produttivo Samsung 7LPP. L'obiettivo di Cadence è consentire a chi crea chip di usare l'avanzato processo produttivo di Samsung e integrare con più rapidità e facilità il supporto GDDR6 all'interno dei propri SoC (system on chip).

La soluzione di Cadence consiste del proprio controller di memoria Denali, di un'interfaccia fisica e di un IP (proprietà intellettutale) di verifica. Il controller e l'interfaccia garantiscono fino a 16 Gbps per pin e hanno un basso bit-error rate (BER) per ridurre la latenza e quindi garantire una maggiore larghezza di banda.

Con questo passaggio tecnico, Cadence può quindi mettere ora a disposizione dei creatori di SoC un pacchetto di riferimento pronto all'uso, in modo che i designer possano replicarne prontamente l'implementazione. La memoria GDDR6, che vediamo anzitutto sulle schede video, troverà spazio in moltissimi settori, dall'automotive al machine learning, fino ai supercomputer (high-performance computing, HPC).

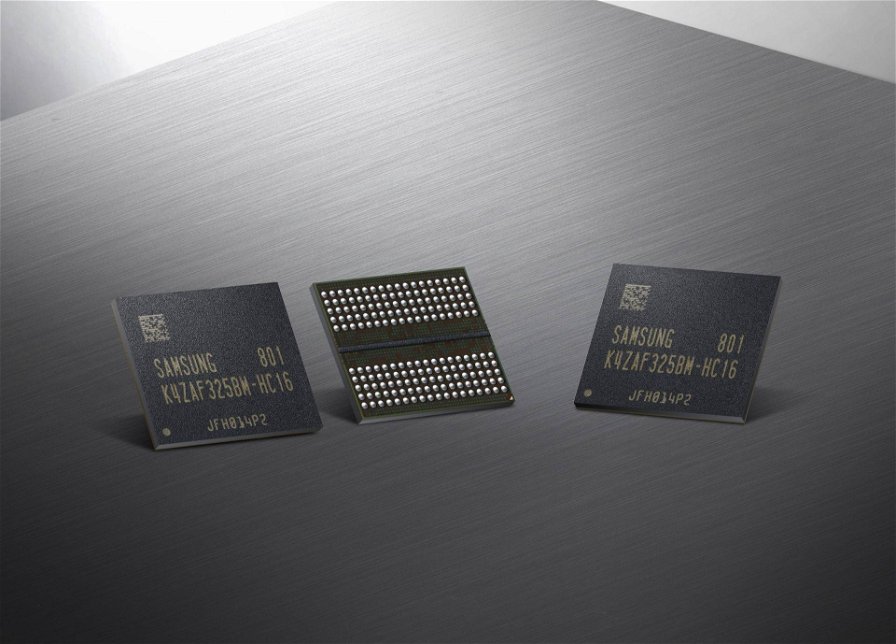

La collaborazione con Cadence è importante anche per Samsung, che essendo il primo produttore di DRAM al mondo ha tutto l'interesse nel rendere il processo produttivo a 7 nanometri LPP (Low Power Plus) il più affidabile e "di riferimento" possibile. L'azienda sudcoreana ha avviato la produzione 7LPP a ottobre, ovviamente in modo molto limitato. Come abbiamo spiegato, si tratta del primo processo a usare la litografia EUV (extreme ultraviolet, ultravioletto estremo) per alcuni layer selezionati.