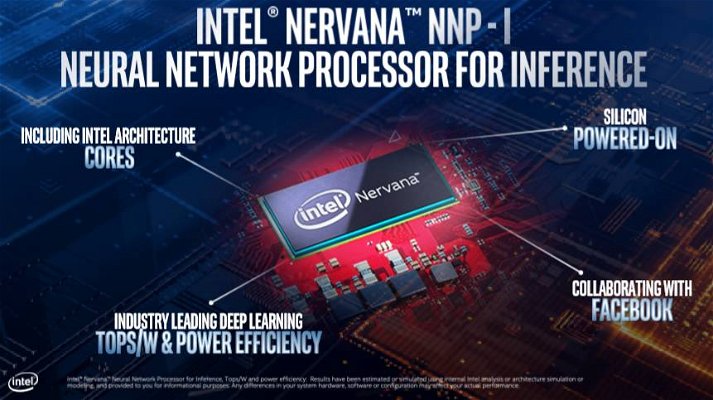

Intel ha annunciato durante l’Israeli Development Center (IDC) Day tenutosi ad Haifa, in Israele, che il suo processore di rete neurale dedicato all’inferenza, chiamato Nervana Neural Network Processor for Inference, o in breve NNP-I, arriverà sotto forma di processore Ice Lake a 10 nanometri modificato, posto su un PCB che s’inserisce all’interno di uno slot M.2, normalmente dedicato all’archiviazione.

Per raggiungere l’obiettivo, Intel ha rimosso parti fondamentali dell’architettura Ice Lake, come il core grafico e i componenti deputati alla visualizzazione, per fare spazio alle unità per accelerare i carichi di intelligenza artificiale. Il dispositivo è comunque sempre basato sul package standard di Ice Lake, con la CPU e il platform controller hub (PCH) affiancati.

L’inferenza permette di usare modelli di IA finiti – ottenuti tramite l’allenamento delle reti neurali usando GPU e FPGA molto potenti – su dispositivi non troppo potenti, al fine di renderli in grado di analizzare le operazioni quotidiane e dai dati raccolti dal mondo circostante. Creare soluzioni per l’inferenza a basso consumo e costo è quindi importante: nel caso dell'acceleratore NNP-I, Intel ha pronosticato l'uso accanto alle CPU Xeon, in modo da sgravarle dai compiti di IA e dedicarle solo ai calcoli generali.

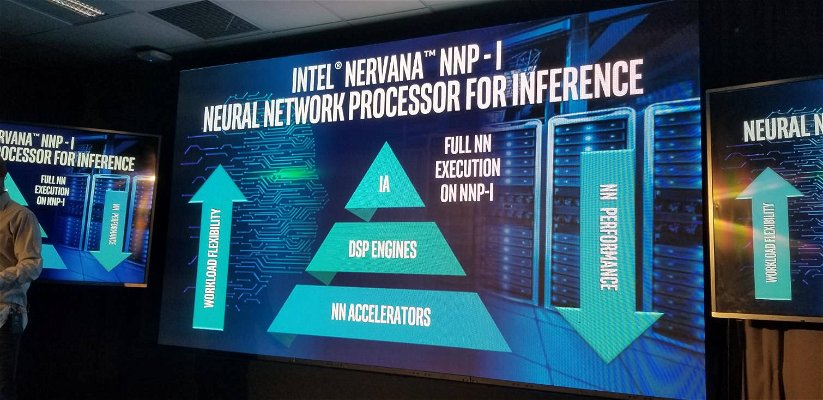

Oltre agli acceleratori Intel ha aggiunto anche degli engine DSP che possono essere usati per algoritmi che non sono perfettamente ottimizzati per i blocchi di accelerazione a funzione fissa. Questo permetterà alla soluzione di mantenere la compatibilità anche se nel campo dell'IA ci saranno evoluzioni.

Intel non ha condiviso dettagli sui blocchi deputati all’accelerazione dell’inteferenza, ma probabilmente si basano su una serie di elementi ripetuti, in modo simile a una GPU (tanti piccoli core). Il sottosistema di memoria di norma dedicato alla GPU Gen11 è in questo caso usato per alimentare i core, e lo stesso ruolo hanno le interconnessioni e le strutture complementari tra le unità.

Lato CPU, abbiamo diversi core x86 – Intel non ha specificato il numero – basati su architettura Sunny Cove. Oren Gershon, general manager di Intel per la parte Inference Products Engineering, ha affermato che l’azienda ha rimosso “alcuni degli altri core” per fare spazio alla componentistica extra, quindi è possibile che non vi siano quattro core x86 su questo dispositivo ma solo due.

Intel può inserire il package in differenti formati, come la versione M.2 fotografata qui sotto, che permettono così l’inserimento all'interno di uno slot M.2 standard su una scheda madre server, o anche su schede aggiuntive più grandi inseribili in uno slot PCIe standard.

A differenza di alcune soluzioni custom progettate per l’IA, come la TPU di Google, questa soluzione offre un’ampia compatibilità hardware, praticamente con qualsiasi server moderno. Anche l’approccio è scalabile: potete aggiungere più NNP-I a un server, specialmente con soluzioni riser PCIe che possono offrire più slot M.2.

Intel ha affermato che NNP-I ha un TDP simile a quello dei processori Ice Lake, il che significa un massimo prossimo ai 28 watt, anche se il limite di 15 watt dell’interfaccia M.2 è qualcosa di cui sicuramente l’azienda avrà tenuto conto. Una NNP-I inserita in schede aggiuntive più grandi può invece operare a valori di TDP più alti, offrendo maggiori prestazioni.

Intel metterà a disposizione del software capace di dirottare i compiti di inferenza interamente della CPU all’acceleratore e poi notificare alla CPU Xeon che il lavoro è pronto. Scaricare questi carichi di lavoro fa sì che lo Xeon non sia costretto a comunicare costantemente lungo il bus PCIe con altri tipi di acceleratori, un compito pesante per la CPU perché genera degli interrupt e richiede il movimento di dati.

Di contro l’NNP-I lavora come un sistema autonomo con il proprio PCH che gli consente di accedere ai dati necessari per svolgere i calcoli.

I carichi di lavoro legati all’IA tendono a richiedere moltissimi dati, il che fa pensare che la connessione PCIe 3.0 x4 non basti. Intel ha assicurato però di aver testato carichi IA legati all’analisi video senza riscontrare limitazioni, che invece esistono per quanto concerne la potenza di calcolo.

I core x86 supportano anche le istruzioni Intel VNNI (DL Boost) che sfruttano AVX-512 per aumentare le prestazioni. Intel ritiene quindi di aver raggiunto un livello di flessibilità massimo, che consente di gestire praticamente qualsiasi tipo di carico di lavoro IA, in particolare quelli inadatti ad altri tipi di core.

Intel metterà a disposizione anche un compilatore in grado di adattare il codice agli acceleratori NNP-I e sta lavorando con Facebook per garantire che il compilatore Glo supporti questo nuovo dispositivo. Non manca inoltre il supporto a tutti i linguaggi standard, come PyTorch e TensorFlow, con nessuna o poche alterazioni.

Secondo Gershon, NNP-I ha un'efficienza “sorprendente, molto meglio di una CPU o GPU di ordini multipli". Le applicazioni di inferenza sono molto più diffuse rispetto all’allenamento nei datacenter, e dispositivi a basso consumo a prezzi accessibili hanno un grande mercato tra i provider di servizi cloud, il che significa che potrebbe diventare un segmento redditizio per Intel. Ovviamente queste soluzioni non saranno acquistabili da tutti, ma Intel si aspetta che i provider di servizi cloud le esporranno tramite istanze.

Intel non è ancora andata oltre le semplici affermazioni, ovvero non le ha supportate con dati prestazionali, ma ha assicurato di essere in fase di sampling con i primi clienti e si aspetta la produzione in volumi entro fine anno. Insomma, ne sapremo di più nei prossimi mesi.