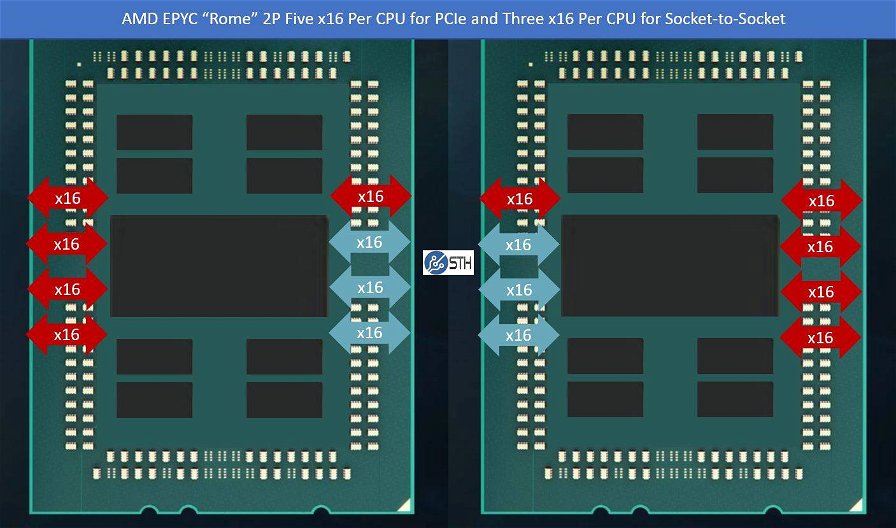

Dopo l'evento Next Horizon dello scorso novembre, AMD non ha più parlato delle caratteristiche dei nuovi processori server EPYC di seconda generazione basati su architettura Zen 2. L'azienda ha dichiarato che un singolo processore EPYC Rome può fornire fino a 128 linee PCI Express 4.0, ma non ha spiegato quante linee mettono a disposizione due processori in un server dual-socket.

In queste ore il sito ServeTheHome.com riporta che, in base ad alcune analisi e voci raccolte, un server dual-socket di CPU EPYC Rome potrebbe fornire fino a 162 linee PCI Express 4.0, ovvero 82 linee in più di una simile configurazione Intel Xeon Cascade Lake AP, che tra l'altro supporta lo standard PCIe 3.0 e non la versione successiva, garantendo quindi un bandwidth inferiore.

La piattaforma Xeon Platinum 9200 (Cascade Lake AP) prevede infatti che ogni CPU abbia 40 linee PCI Express 3.0 per un totale di 80 linee, mentre le altre CPU Xeon Scalable di seconda generazione (Cascade Lake SP) garantiscono 48 linee PCIe 3.0 ciascuna, per un totale di 96 linee.

Secondo Patrick Kennedy di ServeTheHome, due CPU EPYC Rome potrebbero esporre 160 linee PCIe 4.0, perché una linea aggiuntiva per CPU (il che significa che in realtà ce ne sarebbero 129 per singolo socket) servirebbe per il collegamento con il baseboard management controller (BMC), un componente chiave delle schede madre server. Un server dual-socket EPY Rome potrebbe quindi avere fino a 16 collegamenti PCIe (2 x 8). Cinque di questi per socket potrebbero essere usati dalla CPU, lasciando gli altri tre al collegamento tra i due socket.

Da questo articolo si è poi acceso un confronto su Twitter con alcuni appassionati, da cui si è arrivati persino a ipotizzare la presenza di un massimo di 190 linee (più due linee BMC). Un quantitativo di linee così elevato consentirebbe di creare server con molti dispositivi PCI Express collegati, tra schede video e soluzioni di archiviazione, assicurando grande flessibilità ai potenziali clienti.

AMD non ha rilasciato commenti sulle teorie esposte nell'articolo, ma secondo ServeTheHome un rappresentante dell'azienda a cui si è rivolto per avere conferme non sembrava "particolarmente entusiasta" della pubblicazione del contenuto. Che Patrick Kennedy ci abbia preso o ci sia andato molto vicino?

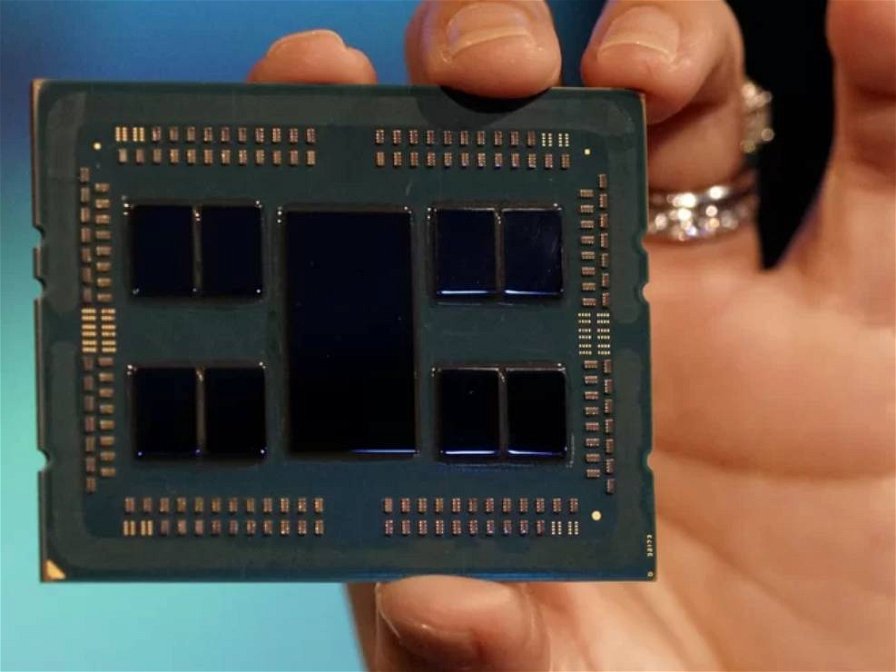

I processori EPYC Rome di seconda generazione offriranno fino a 64 core x86 (con SMT per un totale di 128 thread) capaci di garantire prestazioni per socket 2 volte maggiori rispetto alla prima generazione di EPYC. Alla base di questa generazione c'è il processo produttivo a 7 nanometri e un design rinnovato, al cui centro c'è un die di input / output prodotto a 14 nanometri (I/O die) circondato da otto "chiplet" realizzati a 7 nanometri, dotati di 8 core ciascuno.

Rispetto alle proposte di punta Cascade Lake sembra quindi che la piattaforma di AMD offrirà non solo più core (64 vs 56), ma anche molte più linee PCI Express, garantendo alle aziende del mondo del cloud computing e dell'intelligenza artificiale la possibilità di farci un po' di tutto. Ne sapremo probabilmente di più a breve, dato che gli EPYC di seconda generazione sono attesi per metà anno.