I ricercatori dell'Università di Cambridge hanno sviluppato il modello architetturale Capability Hardware Enhanced RISC Instructions (CHERI) per oltre un decennio. Recentemente, ARM ha annunciato di aver reso disponibile il primo hardware che integra un SoC basato sull'architettura CHERI, raggiungendo un traguardo importante per il suo programma quinquennale Morello, e che è già stato inviato a società interessate come Microsoft e Google.

È difficile negare che un maggiore sforzo deve essere messo nella sicurezza dei dispositivi, dato che ultimamente si legge sempre più spesso di hack, violazioni e furti digitali di qualche tipo. I ricercatori dell'Università di Cambridge e di ARM hanno pianificato con attenzione una nuova architettura da impiegare nei SoC basati su ARM per rendere molto più difficile la vita agli hacker che desiderano accedere ai sistemi, in particolare alla memoria (più di due terzi delle vulnerabilità risolte attraverso patch riguardano problemi di sicurezza della memoria, secondo una ricerca di Microsoft e Google).

Centrale per il programma Morello sono i SoC basati su ARM e le schede dimostrative che vengono inviate a partner come Microsoft e Google, così come altre figure importanti di tutta l'industria e il mondo accademico attraverso l'iniziativa UKRI Digital Security by Design (DSbD). Maggiori informazioni sulla distribuzione di queste schede saranno diffuse da Innovate UK nel corso di un webinar che si terrà il prossimo 25 gennaio.

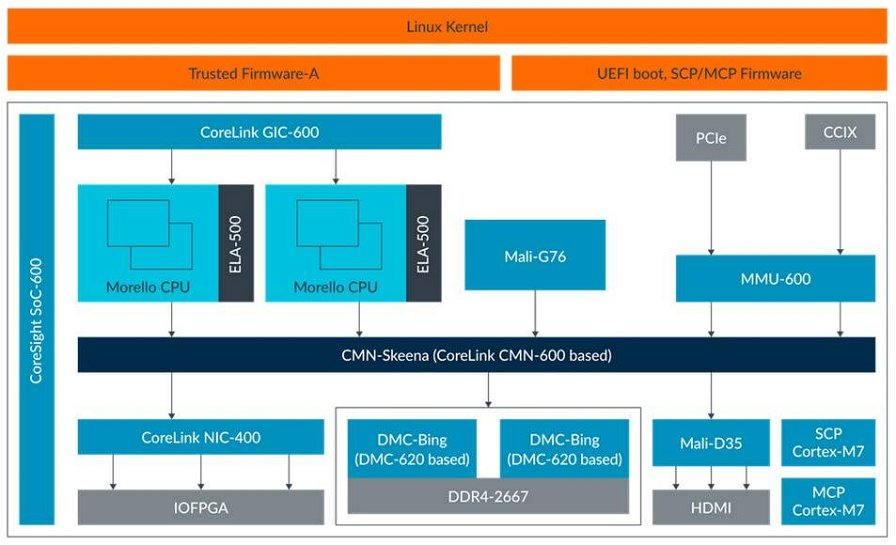

Un altro post sul blog di ARM fornisce più dettagli inerenti alla tecnologia dietro al Morello Technology Demonstrator. Viene rivelato che l'architettura del prototipo è un'estensione di ARM v8.2a 64-bit che permette una protezione della memoria a grana fine e una compartimentazione del software altamente scalabile grazie a CHERI. Il SoC Morello è basato sul design ARM Neoverse N1 two-cluster quad-core costruito su TMSC N7. ARM afferma di aver raggiunto l'obiettivo di integrazione di CHERI per soddisfare le proprie tempistiche e che si potrebbe fare ancora qualcosa nell'ottimizzazione della potenza e delle prestazioni, ma è felice che l'hardware della demo funzioni a 2,5GHz. Sono state conservate molte caratteristiche Neoverse, come l'SCP (System Control Processor), MCP (Manageability Control Processor), Mali GPU, Mali DPU e così via.

Il SBC Morello è completato da elementi essenziali come la RAM e PCIe, più l'adattatore di debug ULINK-Plus di ARM per consentire i test più approfonditi. Le schede prototipo costituiscono un importante passo in avanti per il programma Morello e agli sviluppatori di software e ai ricercatori di sicurezza sono stati dati i prossimi due anni per verificare le capacità del SoC e della scheda. Se tutto andrà come previsto, il programma Morello darà vita a una nuova linea di SoC ARM che offriranno un design più sicuro per i dispositivi del futuro.