TSMC si sta preparando ad abbassare i prezzi per la produzione a 3nm allo scopo di stimolare l'interesse dei progettisti di chip. Sebbene la famiglia di processi di fabbricazione N3 (classe 3nm) introduca una serie di vantaggi in termini di prestazioni e potenza, i costi elevati del nodo N3 ostacolano la sua adozione.

Sembra che la tecnologia di produzione iniziale N3 di TSMC, nota anche come N3B, sarà utilizzata solo da Apple, poiché l'azienda costituisce il più grande cliente della fonderia ed è disposta a adottare nodi all'avanguardia prima degli altri. N3 è una tecnologia costosa da utilizzare, poiché impiega ampiamente la litografia ultravioletta estrema (EUV) per un massimo di 25 strati e ogni scanner EUV costa attualmente 150-200 milioni di dollari.

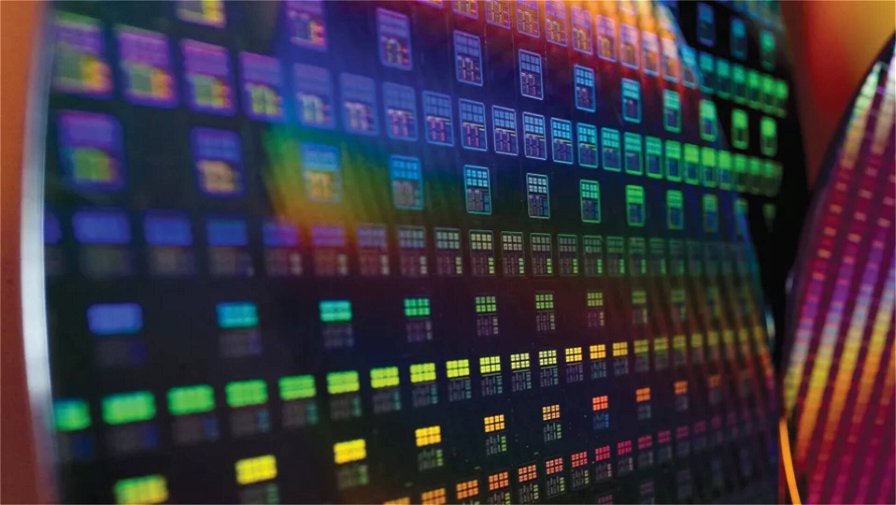

Secondo alcune fonti, TSMC potrebbe richiedere un prezzo fino a 20.000 dollari per wafer N3, rispetto ai 16.000 per wafer N5. Questo significa che la produzione di chip continua ad aumentare di costo e, di conseguenza, aziende come AMD, Broadcom, MediaTek, NVIDIA e Qualcomm potrebbero vedere una riduzione dei loro profitti. A causa di ciò, gli sviluppatori di chip stanno considerando come creare progetti avanzati e utilizzare i nodi più recenti in modo più efficiente.

Szeho Ng, analista di China Renaissance, ha affermato:

Riteniamo che l'accelerazione significativa di N3 avverrà nel secondo semestre del 2023, quando sarà pronta la versione ottimizzata, N3E. I suoi principali clienti nei settori HPC (ad esempio AMD, Intel), smartphone (ad esempio QCOM, MTK) e ASIC (ad esempio MRVL, AVGO, GUC) probabilmente rimarranno in N4/5 e sceglieranno l'N3E come primo passo nella classe N3, a nostro avviso. Nel frattempo, riteniamo che l'adozione della classe N3 (alias N3B) sarà in gran parte limitata ai prodotti Apple.

TSMC starebbe considerando di abbassare i prezzi per la produzione sui nodi di classe N3 per aumentare l'interesse delle aziende. In particolare, il processo N3E utilizza l'EUV solo per un massimo di 19 strati e presenta una minore complessità in termini di produzione, rendendolo più economico. L'N3E non offre vantaggi rispetto all'N5 per quanto riguarda la scalabilità delle celle SRAM e le dimensioni dei die sono maggiori rispetto a quelli prodotti su N3/N3B. Oltre al fattore economico, c'è un altro grosso problema: i bassi rendimenti. Infatti, stando a quanto riferito da DigiTimes, questi ultimi potrebbero essere addirittura inferiori al 50%, nonostante le stime precedenti parlassero di valori compresi tra il 60% e l’80%.