Lanciato lo scorso marzo, il SoC Apple M1 Ultra sfrutta un’interfaccia di connessione die-to-die che permette di collegare due chip M1 Max, ottenendo praticamente il doppio delle prestazioni, senza i compromessi che si hanno di norma quando si connette un chip a un altro attraverso le linee presenti sulla scheda madre. L'architettura di packaging personalizzata prende il nome di UltraFusion, di cui i colleghi di DigiTimes hanno offerto in passato informazioni più precise, che trovate in questo nostro precedente articolo.

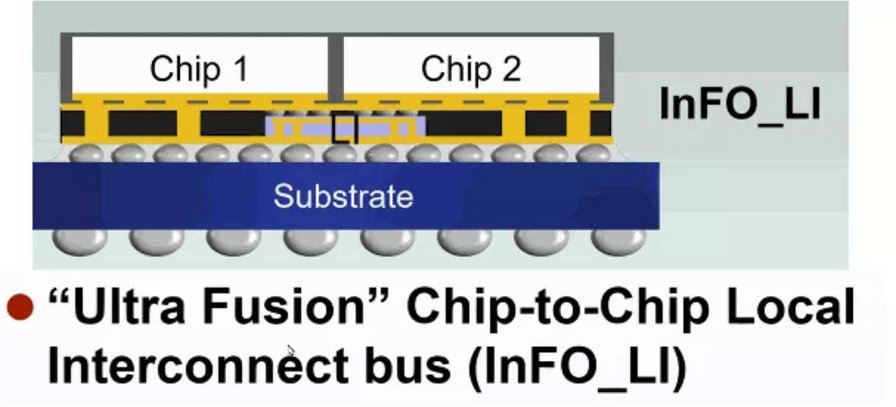

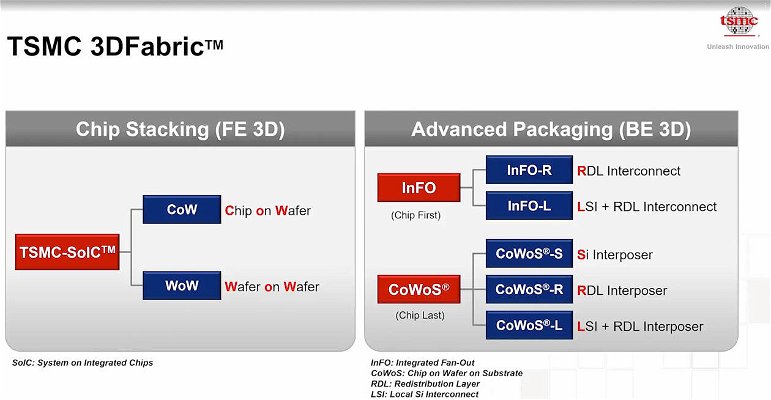

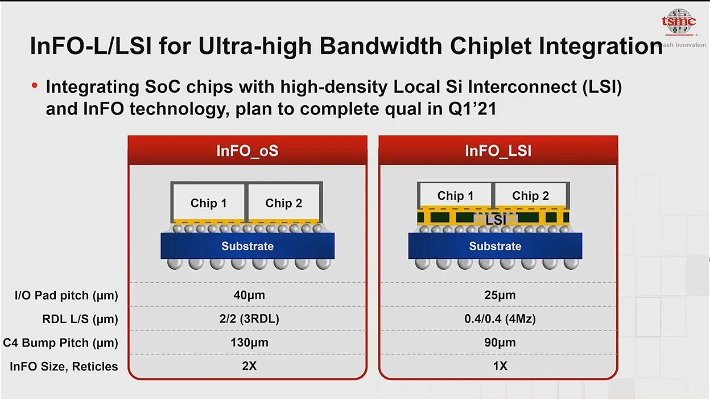

Stando a DigiTimes, l'azienda di Cupertino ha impiegato il processo di packaging 2,5D CoWoS-S (chip-on-wafer-on-substrate with silicon interposer) di TSMC, ma a quanto pare ciò non è corretto. Infatti, secondo una presentazione tenuta dalla stessa TSMC all'International Symposium on 3D IC and Heterogeneous Integration, Apple usa la tecnologia Integrated Fan-Out (InFO) con Local Silicon Interconnect (LSI) e un Redistribution Layer (RDL).

Successivamente ricondivisa da Tom Wassick, un ingegnere esperto nel packaging dei semiconduttori, la slide mostra che UltraFusion usa una ponte di silicio passivo per collegare un chip M1 Max all'altro, che può essere realizzato in vari modi. Mentre CoWoS-S usa un costoso interposer, InFO_LI impiega interconnessioni di silicio localizzate sotto più matrici, in modo del tutto simile all'Embedded Die Interconnect Bridge (EMIB) di Intel.

Ricordiamo che M1 Ultra è quasi 8 volte più veloce di M1 e mette a disposizione un massimo di 20 core CPU, suddivisi in 14 core ad alte prestazioni e 6 core ad alta efficienza, un massimo di 128GB di memoria RAM (64 GB per chip), il doppio dei canali e una larghezza di banda che arriva a 800GB/s. Il comparto grafico può contare su una GPU con 64 core, mentre il Neural Engine è dotato di 32 core per la gestione di carichi IA.