Kioxia (ex Toshiba Memory) ha messo a punto Twin BiCS Flash, una nuova tecnologia per incrementare la densità di archiviazione della memoria NAND. Essenzialmente, la soluzione consente ai chip di memoria di avere celle molto più piccole e più bit per cella, due aspetti che portano a una densità di memoria maggiore.

Twin BiCS Flash rappresenta un potenziale candidato per unità di archiviazione in grado di contenere più di quattro bit per cella (QLC). Al Flash Memory Summit 2019 di agosto, l’allora Toshiba Memory, aveva discusso dei suoi piani per il futuro, ma ora l’azienda ha pubblicamente annunciato la prima “struttura split-gate semicircolare di celle di memoria flash tridimensionali” al mondo.

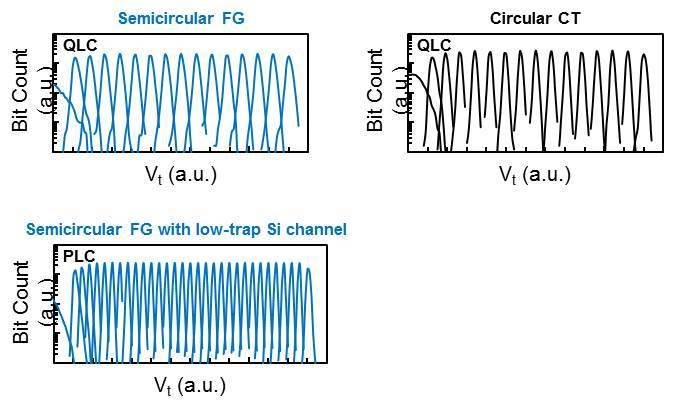

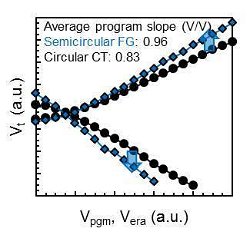

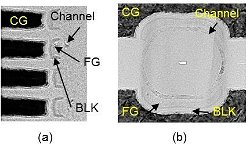

Il nome Twin BiCS Flash richiama quello BiCS Flash, ossia l’attuale tecnologia 3D che Kioxia sviluppa e produce con il partner Western Digital. A differenza della soluzione attuale, basata su celle circolari “charge trap” (CT), ossia che intrappolano la carica, la nuova Twin BiCS Flash adotta celle floating gate semicircolari (FG).

La nuova struttura espande la finestra di programmazione della cella, anche se le celle sono più piccole rispetto alla tecnologia CT. Di conseguenza la nuova tecnologia si candida a succedere alla tecnologia NAND QLC, anche se non è chiaro al momento se diventerà una soluzione penta-level cell (PLC) o qualcos'altro.

Ciò che deve restarci da questo annuncio è che Kioxia ha presentato una nuova tecnologia per aumentare la densità della memoria NAND flash, il che spiana la strada a SSD e soluzioni di archiviazione sempre più capienti, piccole e meno costose.

Di norma ci sono tre modi per aumentare la densità della memoria NAND flash. Il primo è aumentare il numero dei layer - strati o livelli - di memoria. Attualmente i produttori hanno creato chip 3D NAND con 96/128 layer, ma stanno pensando a come spingersi fino a 500/800 layer in futuro.Il secondo è quello di aumentare il numero di bit per cella, e l’abbiamo visto in tutti questi anni passando dalle NAND SLC con 1 bit per cella fino alle attuali QLC con 4 bit per cella. Il problema di questo percorso è incide sull’affidabilità e la resistenza in scrittura della memoria. Infine, il terzo modo è quello di ridurre la dimensione della cella in modo che più celle possano occupare un singolo layer.

La Twin BiCS Flash di Kioxia abbraccia la seconda e terza via, in quanto secondo l'azienda superare i 100 layer apporta un miglioramento minimo e impone dei compromessi - ciononostante aspettatevi NAND con più di 100 layer anche da Kioxia. La memoria Twin BiCS Flash, per quanto sia stata ufficialmente annunciata, è ancora lontana dal debutto. Prima di lei assisteremo sicuramente il prossimo anno al debutto della BiCS 5.