L’European Processor Initiative (EPI) ha lavorato per fornire indipendenza all'Unione Europea nel campo del calcolo ad alte prestazioni (HPC) tramite lo sviluppo di acceleratori personalizzati basati su RISC-V. Chiamato European Processor Accelerator (EPAC), il chip è stato progettato per il calcolo ad alta efficienza e ad alto rendimento ed è attualmente in fase di test presso i laboratori di EPI.

L'European Processor Initiative è iniziato come un progetto di 28 partner provenienti da 10 paesi europei per dotare l'Unione Europea di processori e tecnologie custom che le consentiranno di diventare una forza indipendente focalizzata su scienza e innovazione. Per raggiungere questo obiettivo, il progetto mira a costruire un sistema HPC completamente personalizzato: "Un segmento chiave delle attività EPI è lo sviluppo e la dimostrazione di IP di processori interamente sviluppati in Europa basati sulla Instruction Set Architecture RISC-V, fornendo core acceleratori efficienti dal punto di vista energetico e ad alto rendimento denominati EPAC (European Processor Accelerators) ."

A quanto pare, il progetto ha mantenuto le sue promesse poiché il primo lotto di chip sta venendo attualmente testato nei laboratori di EPI. I processori RISC-V sono stati progettati per contenere più acceleratori multi-purpose, tutti incentrati sull'ISA RISC-V e sui suoi principi di design. Il processore contiene quattro tile di Vector Processing Unit (VPU) costituite da core Avispado RISC-V progettato da SemiDynamics e da elementi di elaborazione vettoriale progettati dal Barcelona Supercomputing Center e dall'Università di Zagabria. In ogni tile, ci sono nodi home e cache L2, che sono i contributi di Chalmers e FORTH.

Per un'ulteriore spinta, ci sono gli acceleratori Stencil e Tensor (STX) progettati da Fraunhofer IIS, ITWM ed ETH Zürich e il processore a precisione variabile (VRP) progettato da CEA LIST. Per mantenere tutti questi componenti collegati, è presente un router Network-on-Chip (NoC) ad alta velocità e SERDES sviluppato da EXTOLL. Altre connessioni off-chip sono finora sconosciute, ma, tuttavia, presumiamo che ci saranno opzioni I/O DDR5 e PCIe Gen4 o Gen5 da utilizzare.

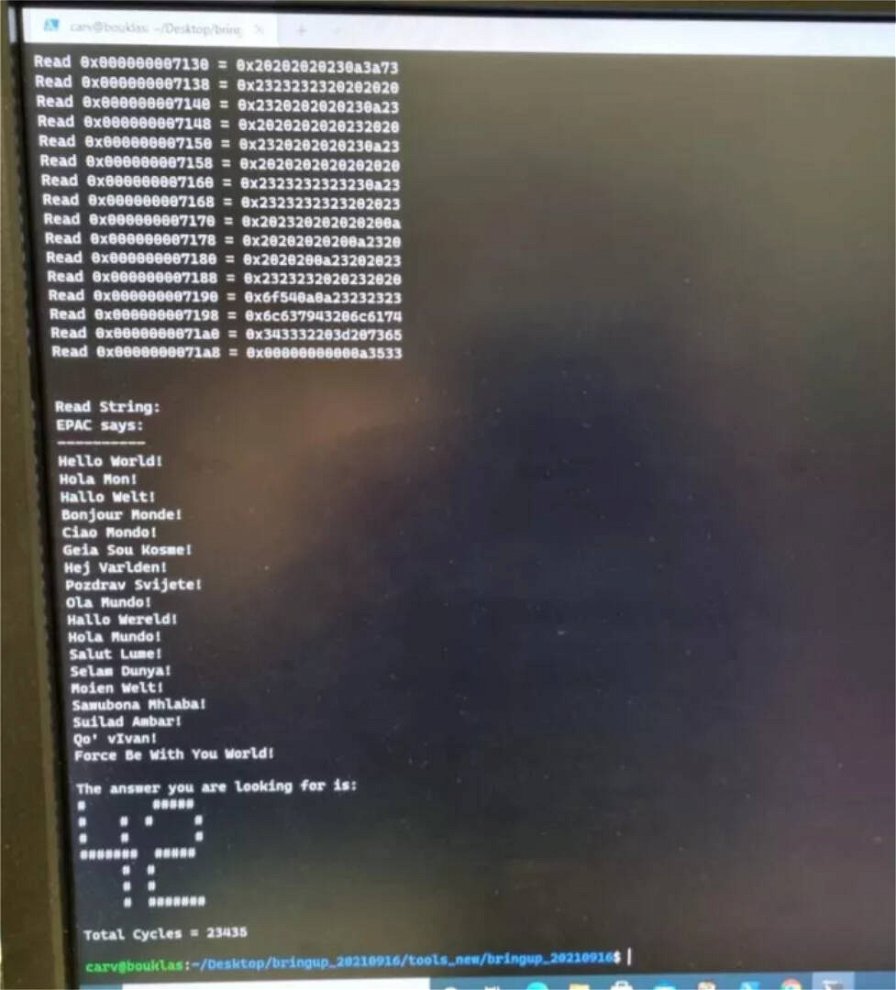

Il chip è stato realizzato su un nodo semiconduttore a bassa potenza FDX a 22nm di GlobalFoundries che è riuscito a effettuare il package del chip in un'area di 26,97 mm² per il die. Il package di test è di tipo FCBGA con 22x22 sfere di saldatura in un array a griglia e il chip ha una frequenza target, finora, di 1GHz. Nell'immagine sottostante, potete vedere il classico "Hello World" in esecuzione sulla nuova piattaforma.

Una volta che tutto sarà pronto, EPI prevede di combinare i chip in un potente sistema HPC utilizzato per tutti i tipi di carichi di lavoro.