Durante il forum europeo OIP di TSMC, Alchip e Ayar Labs hanno presentato un motore di input/output ottico completamente integrato nel package, progettato per abilitare connettività fotonica negli acceleratori AI di prossima generazione. La soluzione, che sfrutta la piattaforma COUPE di TSMC, rappresenta un tentativo di democratizzare l'accesso a tecnologie finora appannaggio esclusivo dei colossi del settore come AMD e NVIDIA.

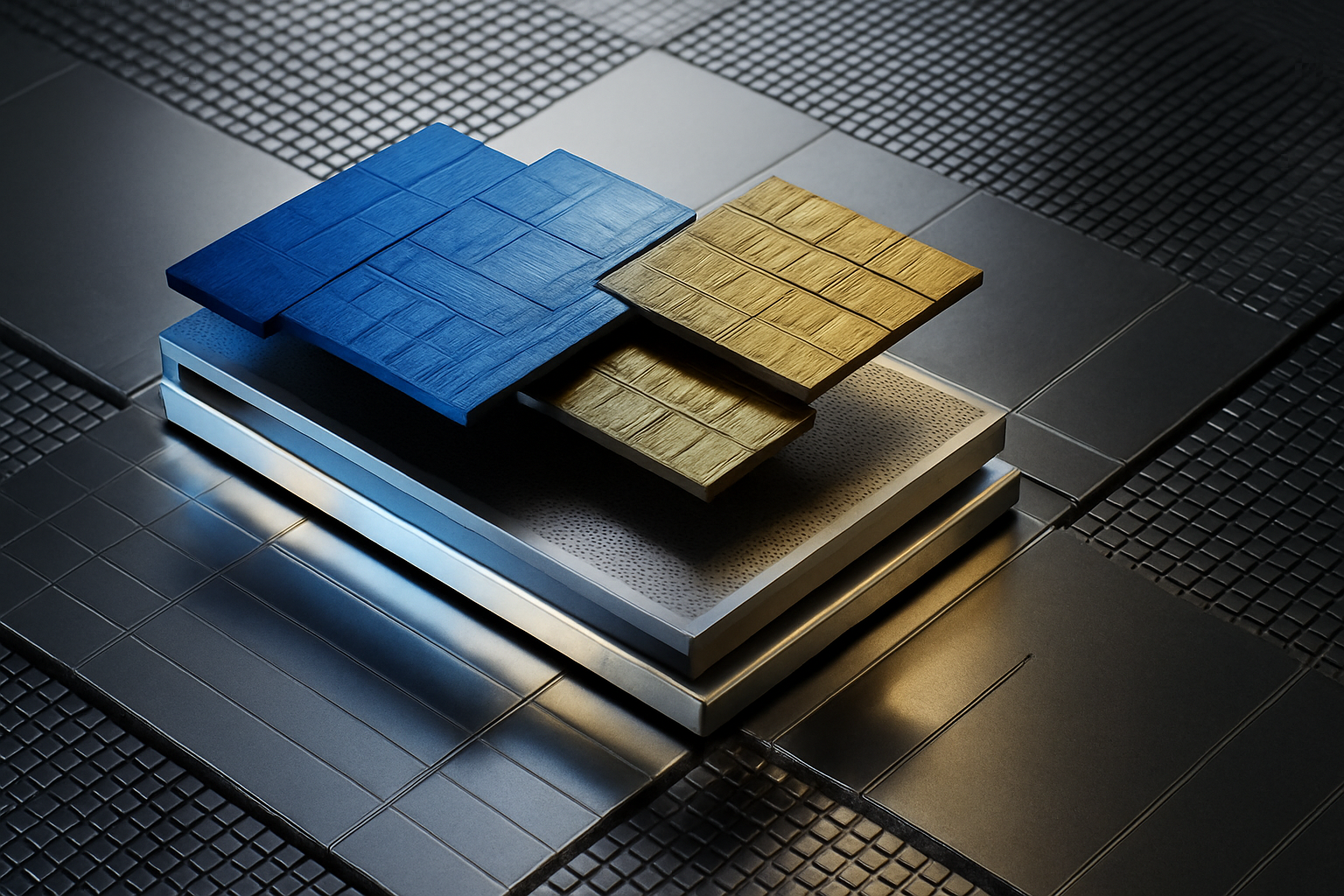

Il sistema si basa su un'architettura a tre chiplet che combina diverse componenti specializzate. Il primo elemento è un chiplet convertitore di protocollo sviluppato da Alchip, capace di terminare l'interfaccia UCIe-A dell'acceleratore e implementare protocolli di scale-up come UALink, PCIe, Ethernet e SUE attraverso UCIe-S in modalità streaming. Questa soluzione offre anche compatibilità con protocolli proprietari incapsulati sull'interfaccia fisica UCIe, garantendo flessibilità per chip che utilizzano standard non convenzionali.

Il secondo componente è un circuito integrato elettrico (EIC) sempre firmato Alchip, responsabile di fornire SerDes a basso consumo energetico, driver di modulazione, temporizzazione e controllo. La terza tessera del puzzle è il chip fotonicamente integrato (PIC) TeraPHY di Ayar Labs, che esegue modulazione e rilevamento ottico utilizzando fotonica al silicio con architettura a microanello. Il PIC viene fornito con connettori in fibra staccabili per facilitare la produzione e offre due opzioni di collegamento: PAM4 CWDM con latenza compresa tra 100 e 200 nanosecondi per hop e un tasso di errore bit inferiore a 10⁻⁶, oppure una soluzione DWDM più avanzata con latenza ridotta a 20-30 nanosecondi per hop e BER inferiore a 10⁻¹².

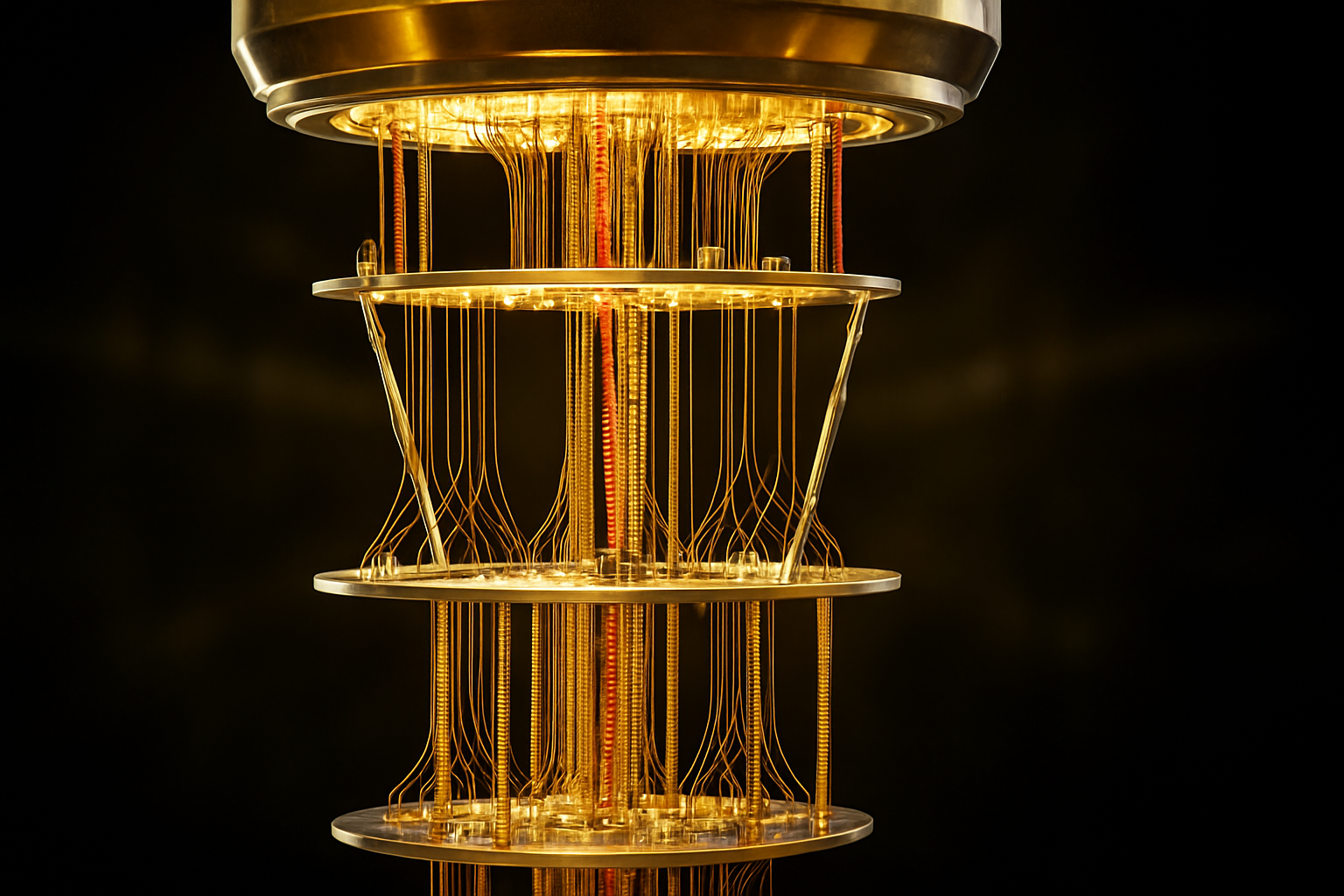

Le prestazioni promesse sono impressionanti: il sottosistema può collegare centinaia di processori distribuiti su più rack, facendoli operare come un unico grande processore. Secondo le aziende coinvolte, la soluzione potrebbe trovare applicazione anche come estensore di memoria, ampliando ulteriormente il suo campo d'impiego oltre ai soli acceleratori AI.

Il design di riferimento presentato include due die acceleratori a reticolo completo, otto stack HBM, quattro chiplet convertitori di protocollo e otto motori ottici TeraPHY di Ayar Labs, tutti montati su un singolo substrato con dispositivi passivi integrati per garantire l'integrità dell'alimentazione. I diagrammi di sistema mostrano la piattaforma in grado di connettere configurazioni XPU-to-XPU, XPU-to-switch e switch-to-switch, abilitando persino espansione di memoria ottica.

L'iniziativa si inserisce nel contesto più ampio della piattaforma Compact Universal Photonic Engine (COUPE) introdotta da TSMC nel 2024, originariamente concepita per produttori di chip di grandi dimensioni con risorse sufficienti per sviluppare circuiti integrati elettronici e fotonici proprietari. La collaborazione tra Alchip e Ayar Labs mira invece a rendere accessibile questa tecnologia anche a sviluppatori di dimensioni più contenute che necessitano di connettività ottica ma non possono permettersi di costruire un sottosistema ottico completo da zero.