Intel sta lavorando attivamente a una rivoluzione architettonica che potrebbe ridefinire il panorama delle CPU nei prossimi anni: l'abbandono della tradizionale struttura ibrida con core Performance ed Efficiency separati in favore di un'architettura a core unificato. La conferma arriva da recenti offerte di lavoro pubblicate dall'azienda, che rivelano l'esistenza di un team dedicato chiamato "Unified Core", attualmente impegnato nelle fasi pre-silicio dello sviluppo. Si tratta di un cambio di paradigma che segna potenzialmente la fine della strategia P/E-core inaugurata con Alder Lake, ma i tempi di implementazione restano ancora lontani.

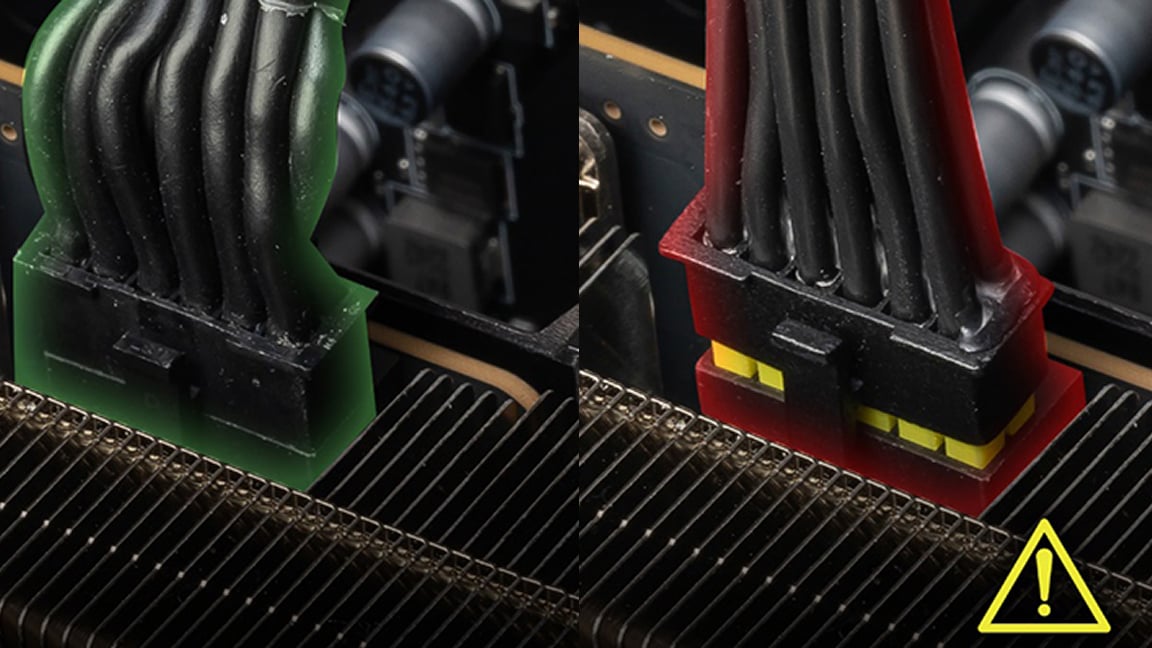

Il concetto di core unificato rappresenta un approccio diametralmente opposto alla filosofia attuale di Intel, che dal 2021 ha adottato una configurazione ibrida ispirata alla tecnologia big.LITTLE di ARM. Invece di combinare core ad alte prestazioni (P-core) con core ad alta efficienza energetica (E-core) basati su microarchitetture differenti, l'architettura unificata punterebbe su un singolo design scalabile capace di adattarsi dinamicamente alle diverse esigenze di carico. L'obiettivo principale è massimizzare il Performance Per Area (PPA), una metrica cruciale che misura l'efficienza nell'utilizzo dello spazio sul die del processore.

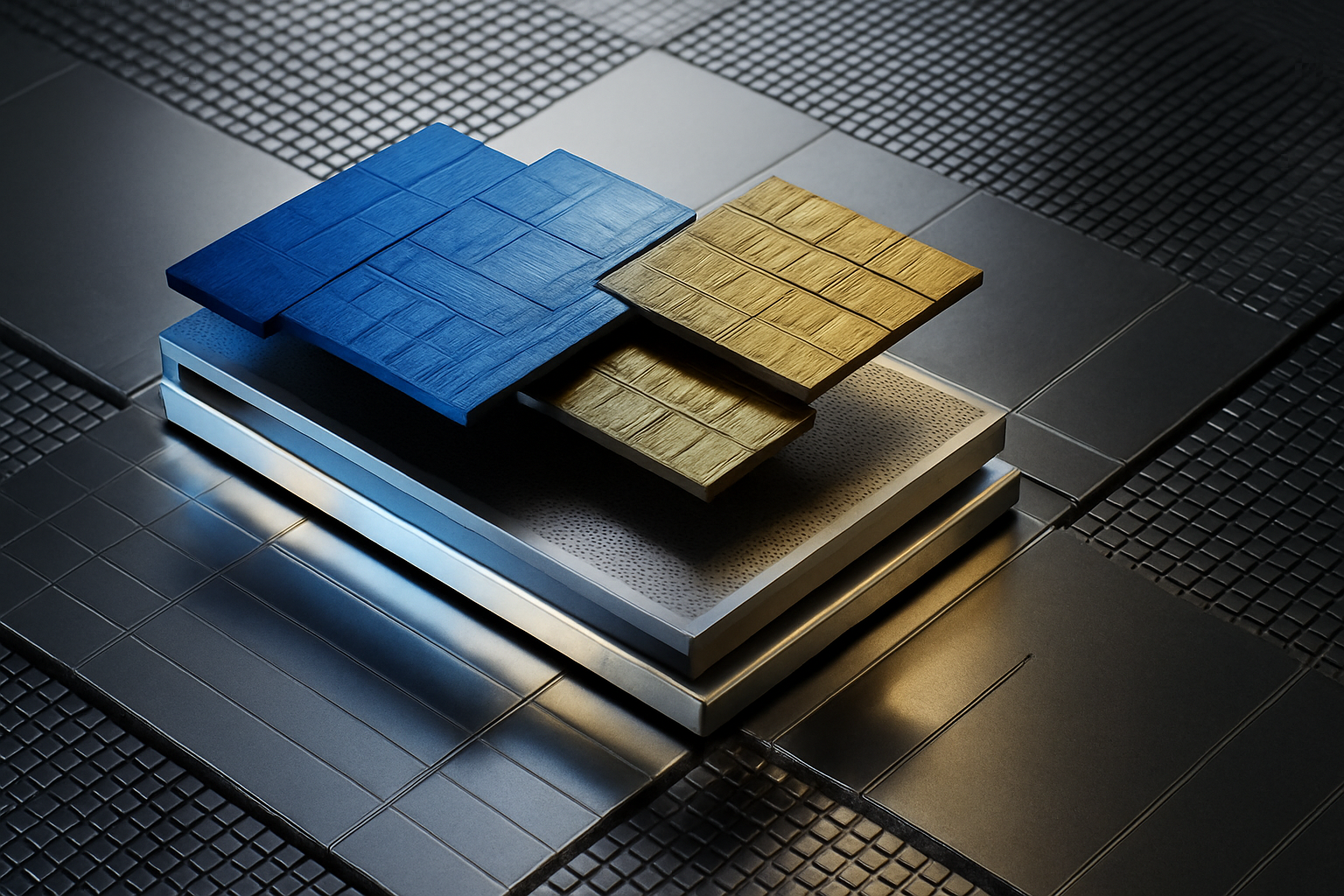

Le limitazioni delle attuali leggi di scala rappresentano il principale ostacolo per i produttori di semiconduttori. Con le microarchitetture separate, il numero di core che può essere integrato su un singolo chip è vincolato da considerazioni di area, consumo energetico e complessità di progettazione. Un core unificato potrebbe teoricamente permettere una densità superiore mantenendo efficienza e prestazioni elevate, sfruttando tecniche di clock gating avanzate e gestione dinamica della frequenza per adattarsi sia a carichi single-thread pesanti che a scenari multi-thread leggeri.

La strategia di Intel non è completamente inedita nel settore. MediaTek ha già sperimentato questo approccio con il SoC Dimensity 9300, che implementa un design "All Big Core" radicale eliminando completamente i core efficiency tradizionali. Anche AMD ha esplorato territori simili con la configurazione Zen5/Zen5c, sebbene in quel caso si tratti più di una variante ottimizzata per densità piuttosto che di una vera architettura unificata. La differenza fondamentale risiede nel fatto che Zen5 e Zen5c condividono la stessa microarchitettura ma con diverse ottimizzazioni fisiche, mentre l'approccio di Intel potrebbe puntare a un design ancora più flessibile.

Le indiscrezioni provenienti da fonti interne a Intel, in particolare da un ingegnere cinese dell'azienda intervistato lo scorso luglio, avevano già anticipato questa direzione strategica. Secondo queste fonti, la generazione Arctic Wolf E-core, attesa con Nova Lake (successore di Panther Lake), rappresenterà l'ultimo capitolo dei core efficiency come li conosciamo oggi. Dopo Nova Lake è previsto Razer Lake, e solo successivamente arriverà Titan Lake, che secondo le speculazioni potrebbe essere la prima architettura a implementare concretamente il core unificato.

Le tempistiche restano incerte, ma considerando i cicli di sviluppo tipici dell'industria dei semiconduttori e le fasi pre-silicio in cui si trova attualmente il progetto, è ragionevole stimare un lancio commerciale non prima del 2028-2029, con la possibilità che slitti fino al 2030. Questo calendario colloca l'architettura unificata a tre generazioni di distanza dalle attuali soluzioni Arrow Lake e Lunar Lake, dando a Intel il tempo necessario per perfezionare una transizione così radicale.

L'offerta di lavoro pubblicata da Intel cerca ingegneri specializzati in progettazione pre-silicio, confermando che il progetto è ancora nelle fasi iniziali di sviluppo e richiede competenze avanzate in simulazione, verifica e ottimizzazione architettonica. Questo significa che molta acqua dovrà ancora passare sotto i ponti prima di vedere processori consumer o datacenter basati su questa tecnologia, e Intel dovrà affrontare sfide tecniche significative legate alla gestione termica, alla scalabilità delle frequenze e all'efficienza energetica in scenari di utilizzo estremamente diversificati.