In occasione del TSMC Technology Symposium 2022, Taiwan Semiconductor Manufacturing Co., meglio nota come TSMC, ha presentato la sua tecnologia di produzione N2 (2nm) che utilizzerà transistor gate-all-around field-effect (GAAFET). Primo nodo dell'azienda a impiegare questa tipologia di transistor, questo nuovo processo offrirà sensibili vantaggi a livello di prestazioni e potenza.

Le innovazioni principali introdotte da N2 riguardano l'uso di transistor nanosheet (GAAFET) e il backside power rail, i quali consentiranno di raggiungere nuovi livelli di efficienza grazie a un miglioramento delle prestazioni per watt. Dal punto di vista tecnico, i transistor nanosheet presentano canali circondati da gate su tutti e quattro i lati, portando a una riduzione delle perdite. Inoltre, i canali possono essere allargati per incrementare la corrente pilota o ridotti per diminuire il consumo di energia.

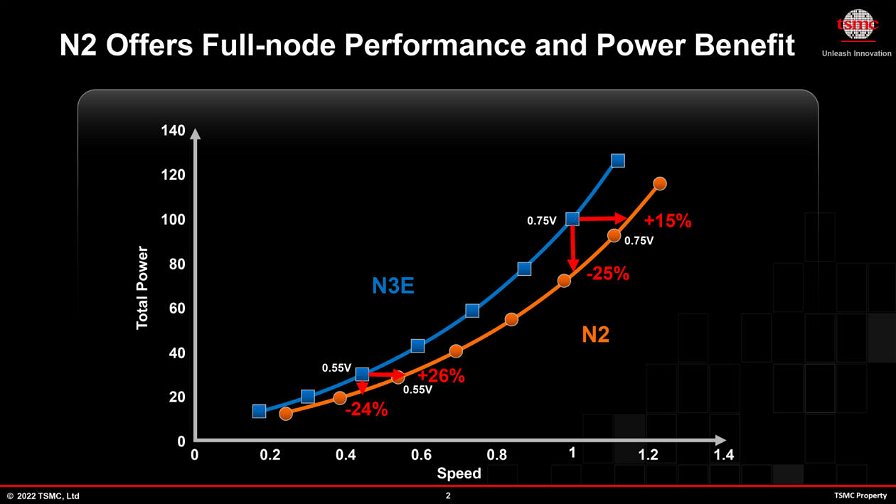

Questa soluzione consente di personalizzare la potenza richiesta e massimizzare l'efficienza, senza contare che l'alimentazione backside costituisce un metodo efficace per combattere le resistenza nel back-end-of-life (BEOL). In linea di massima, si parta di prestazioni maggiori del 10-15% a parità di potenza e complessità, nonché consumi inferiori del 25-30% rispetto al nodo N3E. Purtroppo, per quanto riguarda la densità, l'incremento si limita a solo 1,1 volte.

| N2 vs N3E | N3E vs N5 | N3 vs N5 | N5 vs N7 | |

|---|---|---|---|---|

| Miglioramento di velocità con la stessa potenza | 10% ~ 15% | +18% | +10% ~ 15% | +15% |

| Riduzione di potenza alla stessa velocità | -23% ~ -30% | -34% | -25% ~ -30% | -30% |

| Densità dei chip | >1.1X | 1.3X | ? | ? |

| Inizio della produzione ad alti volumi | H2 2025 | Q2/Q3 2023 | H2 2022 | Q2 2022 |

TSMC propone il suo nodo 2N per molteplici applicazioni, dalle GPU ai SoC per dispositivi mobile. La società ha anche fatto riferimento all'integrazione di chiplet, il che fa supporre che 2N verrà usato anche per package multi-chiplet per ottimizzare costi e performance. La produzione in grandi volumi è prevista per la seconda metà del 2025, quindi ci aspettiamo di vedere i primi prodotti dotati di chip realizzati su 2N per la fine dello stesso anno o addirittura nel 2026.