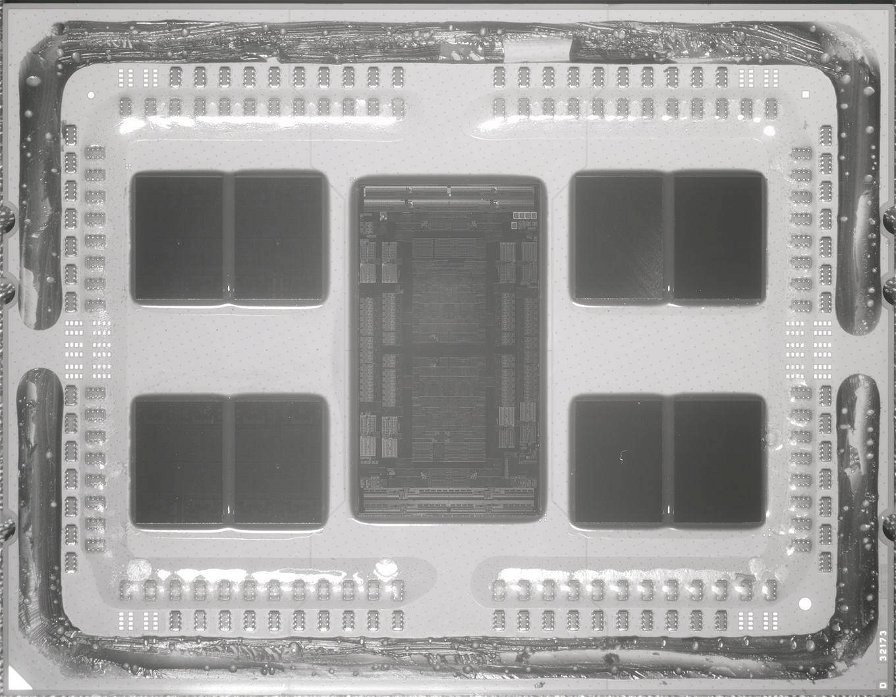

L'utente OC_Burner del forum di HardwareLuxx, meglio noto come Fritzchens Fritz, ha pubblicato le foto dei vari "die" che compongono una CPU AMD EPYC Rome con 64 core, ossia la seconda generazione di CPU server EPYC basata su architetture Zen 2 a 7 nanometri.

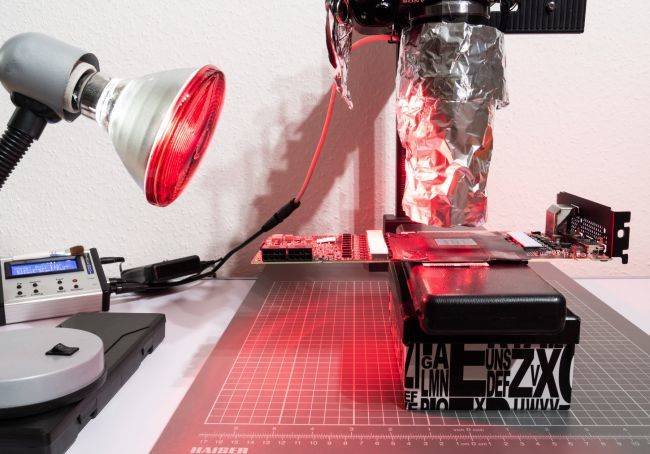

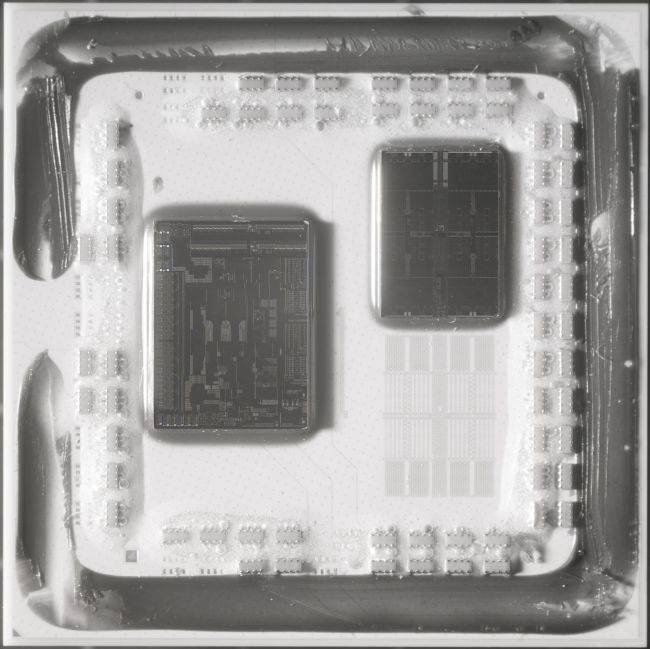

L’immagine qui sopra può sembrarvi familiare, visto che la CPU senza l’HIS (heatspreader) è stata mostrata più volte, ma la differenza in questo caso è che si tratta di una foto ottenuta in un’altra lunghezza d’onda rispetto al visibile: l’infrarosso. Il silicio esposto agli infrarossi diventa quasi "trasparente", permettendo la visione all'interno al die, in modo da apprezzarne le diverse strutture.

La parte centrale del chip è rappresentata dall'I/O die, mentre gli 8 chip intorno sono i CCD, noti anche come Core Complex Die, vale a dire i die che contengono i core fisici della CPU. Per migliorare la visione dei componenti interni OC_Burner ha anche "levigato" leggermente parte del silicio per esporre meglio gli strati sottostanti alla telecamera.

Ovviamente il chip usato per gli scatti fotografici, che possiamo paragonare a un servizio di Playboy per appassionati di hardware molto soli, è un engineering sample oppure una CPU non funzionante.

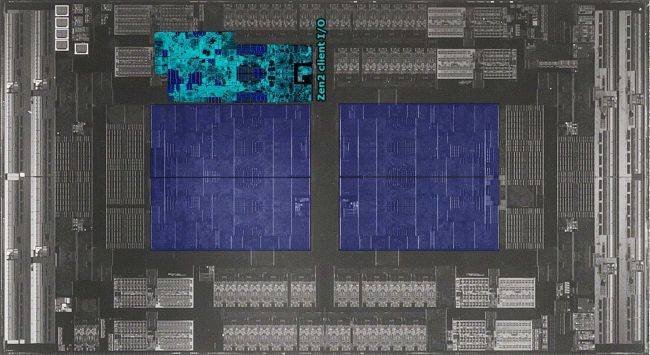

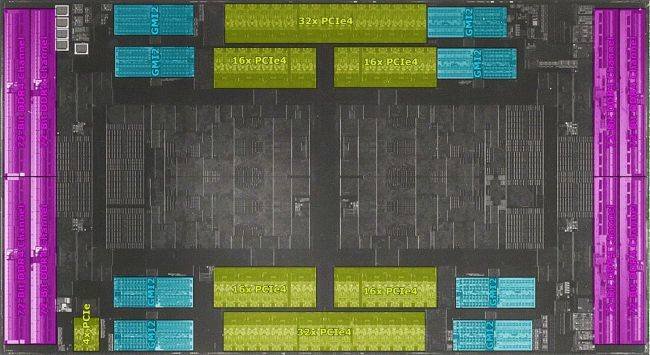

L’I/O die sulla CPU AMD EPYC Rome è significativamente più grande di quello delle CPU Matisse (AMD Ryzen 3000), e non è una sorpresa, visto che deve gestire molti più core, canali di memoria, ecc. L'utente Locuza su Twitter ha analizzato le immagini e identificato tutti i singoli componenti presenti nel silicio, come illustrato nelle immagini seguenti. L'I/O die sulle CPU EPYC Rome ha un numero di transistor pari a 8,34 miliardi e misura 416 mm2.

L’I/O die è essenzialmente il cuore della CPU e al suo interno è possibile vedere i componenti per la gestione dei canali PCI Express, quelli della memoria DDR4 e la Global Memory Interconnect.

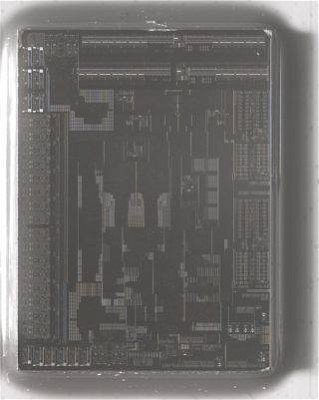

I CCD non sono stati raffigurati in dettaglio su questa CPU EPYC, ma sono identici a quelli che si trovano sui Ryzen 3000, quindi quelli di seguito sono scatti agli infrarossi di un Ryzen 5 3600. A sinistra è possibile vedere l'I/O die, notevolmente più piccolo di quello di EPYC Rome. In questo caso conta infatti su 2,09 miliardi di transistor e misura circa 125 mm2, più o meno un quarto dell'I/O die di EPYC Rome.

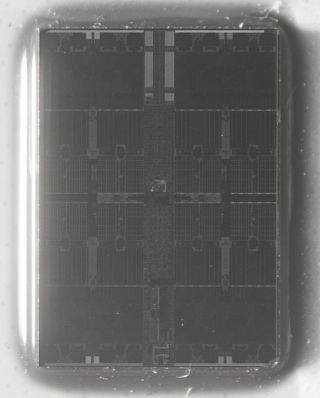

Il CCD invece si trova sulla destra e nell'immagine ha lo strato opaco rimosso, a differenza dei CCD della prima immagine, quindi è possibile vederne l'interno. I CCD nelle due CPU sono identici, tranne ovviamente che su Ryzen 5 due core sono disabilitati e che EPYC non ha uno ma ben otto CCD. Ogni CCD integra 3,9 miliardi di transistor e misura 74 mm2.

Se fotografaste un Ryzen 9 3900X vedreste non uno ma due CCD. Sul Ryzen 5 in ogni caso si può vedere lo spazio nel quale si troverebbe il secondo CCD. Dando un’occhiata più ravvicinata al CCD, è chiaro come sia composto da 8 core centrali, con la cache L2 e L3 sopra e sotto i core.

Sommando il numero di transistor degli otto CCD del chip EPYC a quelli dell’I/O die si ottiene un totale di 39,54 miliardi di transistor e una superficie di silicio totale di 1008 mm2. Numeri da capogiro. E se questo non vi fa apprezzare la meraviglia ingegneristica che c'è dietro i microprocessori, francamente non sappiamo più cosa potrebbe stupirvi...

| Numero transistor | Dimensione die | |

| CCD | 3,9 miliardi | 74 mm² |

| I/O die (EPYC) | 8,34 miliardi | 416 mm² |

| I/O die (Ryzen) | 2,09 miliardi | 125 mm² |

| Totale EPYC | 39,54 miliardi | 1.008 mm² |

| Totale Ryzen 5 | 5,99 miliardi | 199 mm² |

| Total Ryzen 9 | 9,89 miliardi | 273 mm² |