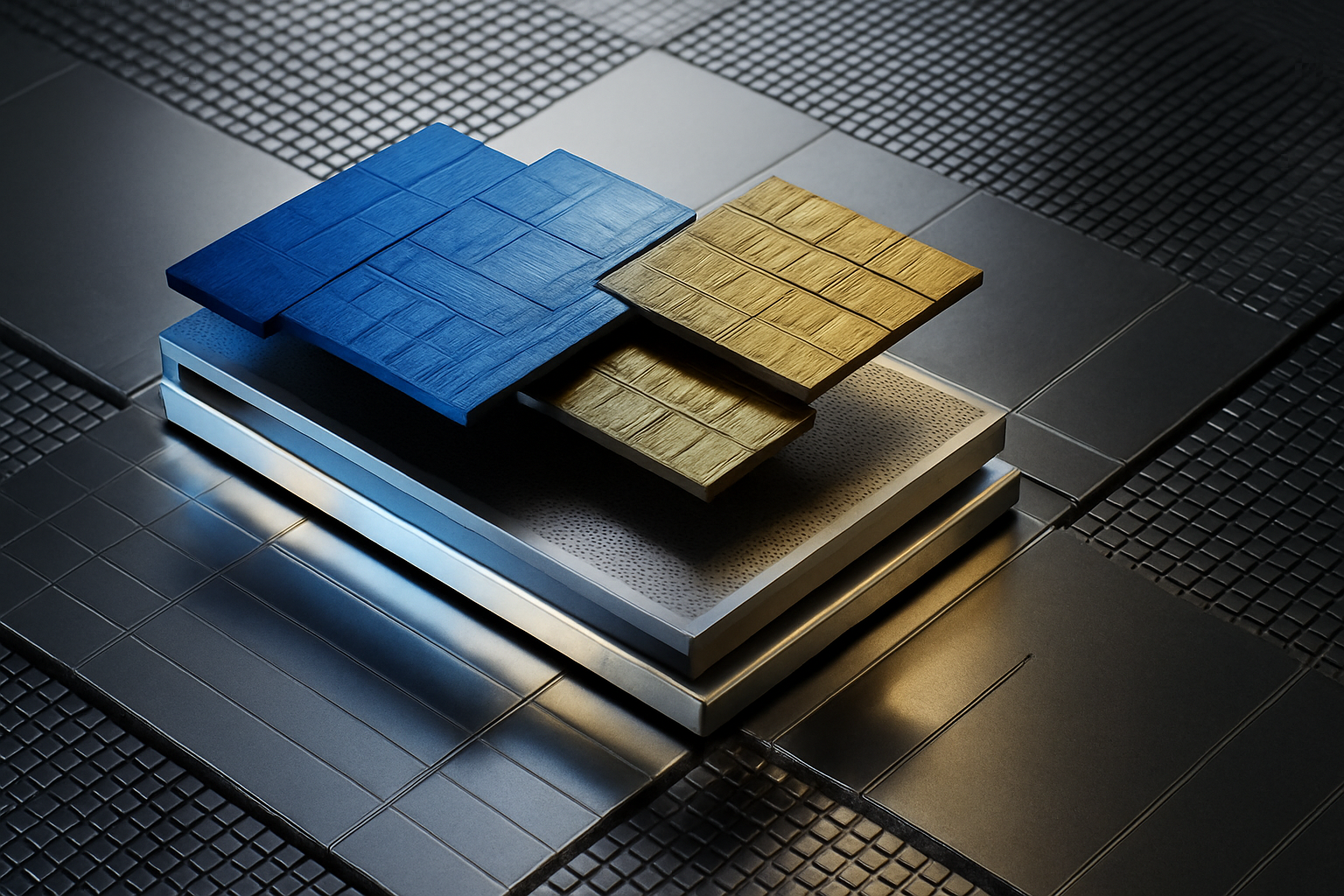

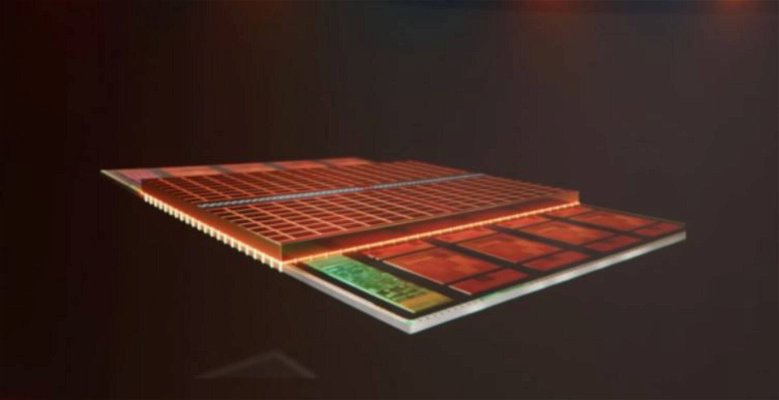

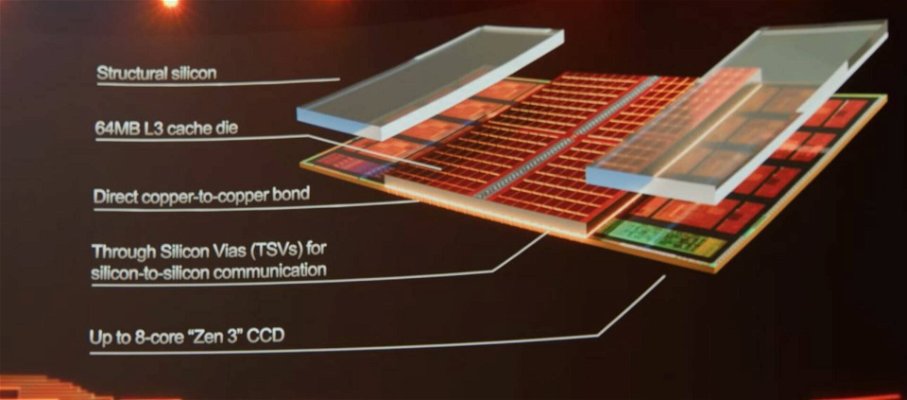

In occasione del Computex 2021, AMD ha annunciato che i chiplet 3D-stacked basati sull'architettura Zen 3 entreranno in produzione quest'anno. Questi ultimi permetteranno di aggiungere ulteriori 64MB di cache SRAM da 7nm (chiamata 3D V-Cache) impilati verticalmente sopra il Core Complex Die (CCD) per triplicare la quantità di cache L3 per i core della CPU. Questa tecnica può fornire fino a 192MB di cache L3 per i processori Ryzen, un miglioramento sostanziale rispetto all'attuale limite di 64MB.

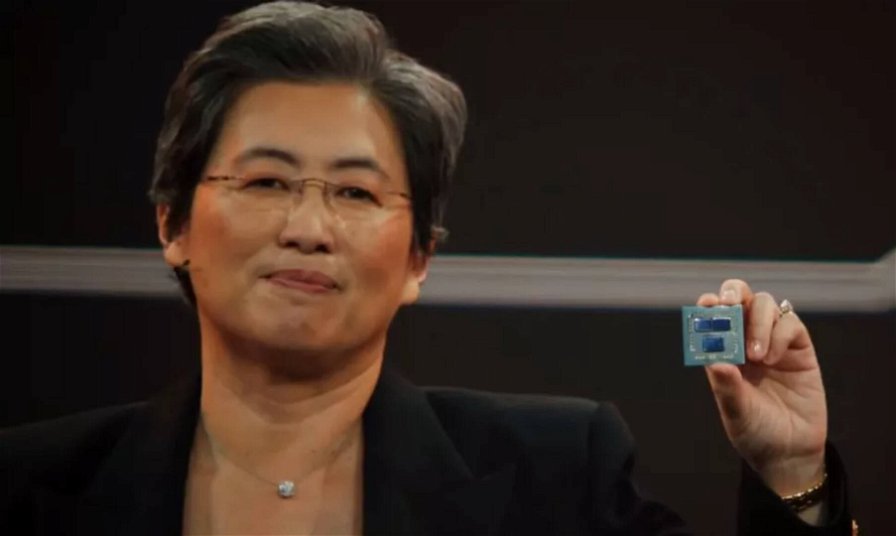

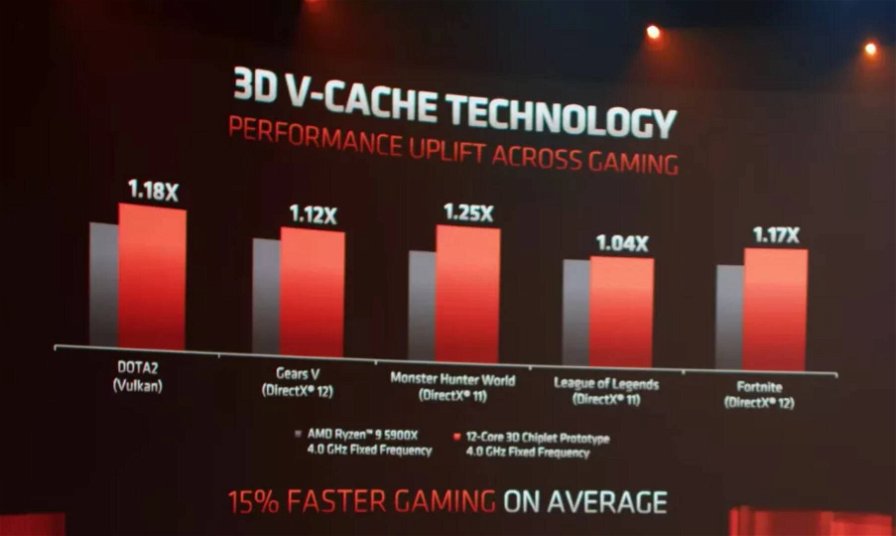

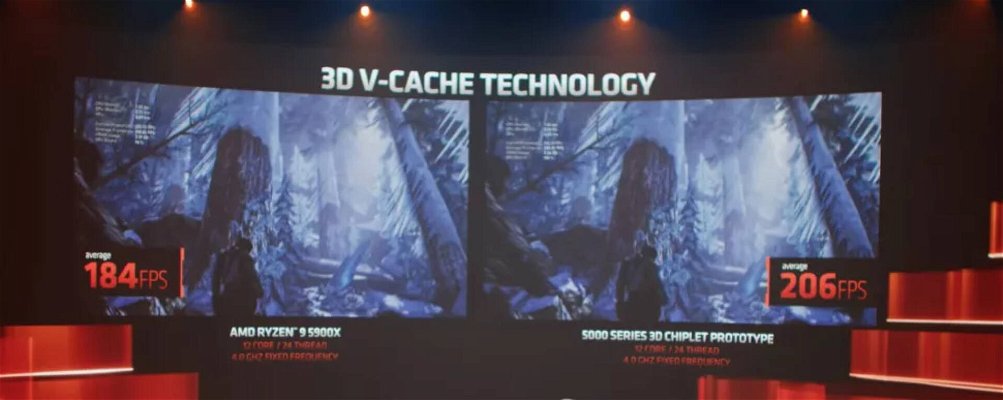

Il CEO di AMD, Lisa Su, ha anche mostrato il prototipo di chip Ryzen 9 5900X funzionante in una dimostrazione che ha messo in evidenza le migliori performance ottenibili in ambito gaming, pari, in questo caso, ad una media del 15% a risoluzione 1080p. Questo è il tipo di guadagno che in genere associamo a una nuova microarchitettura CPU e/o nodo di processo, ma AMD ha compiuto questa impresa con lo stesso nodo a 7nm e la medesima architettura Zen 3 già utilizzata sugli attuali modelli Ryzen serie 5000.

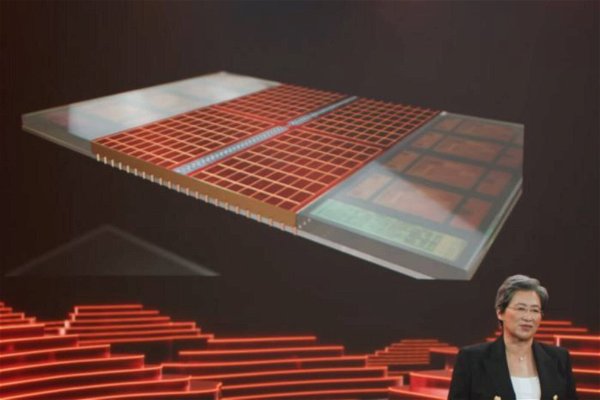

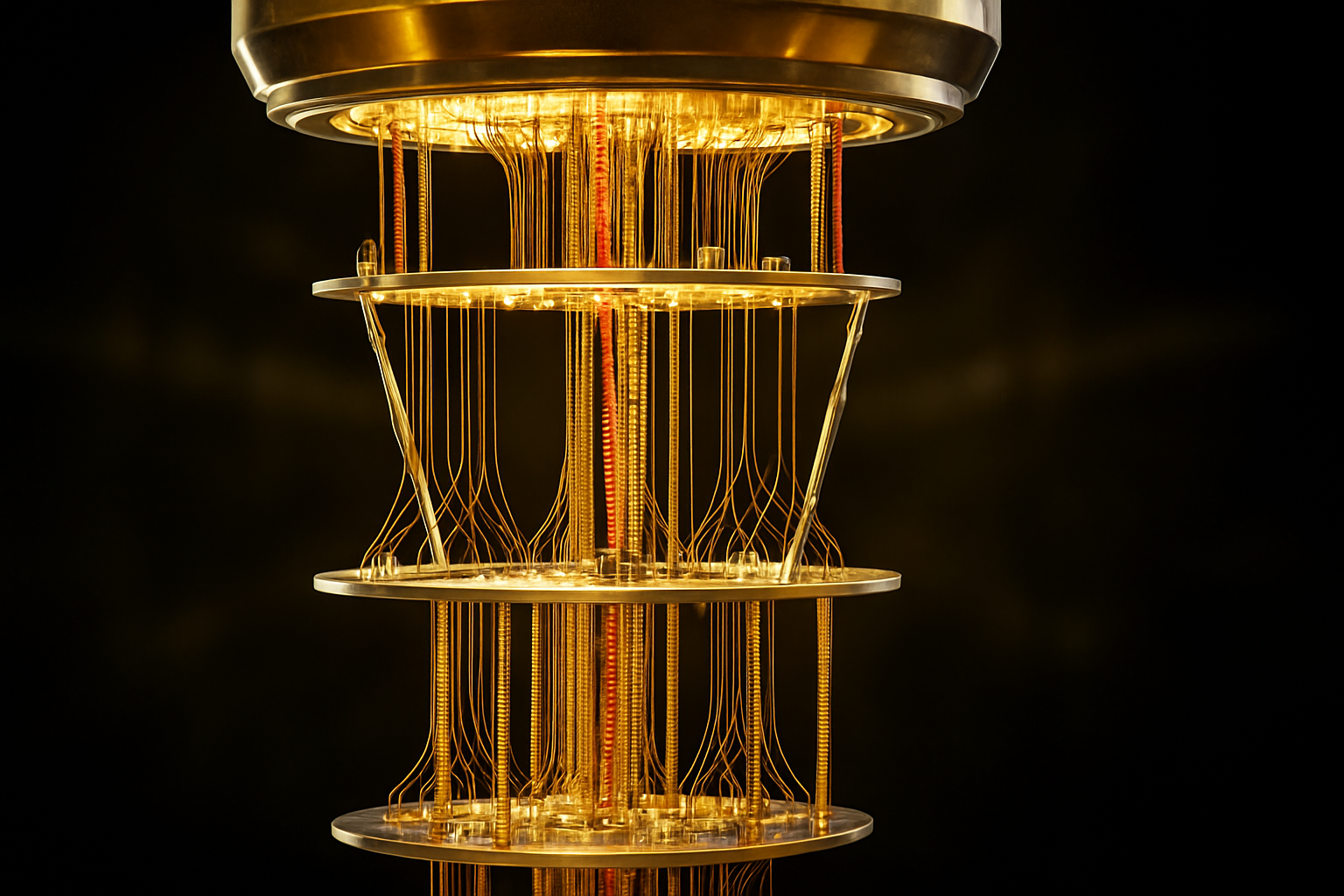

AMD lega la cache 3D alla parte superiore del CCD Ryzen con TSV (Through Silicon Vias) che consentono di arrivare sino a 2TB/s di larghezza di banda tra il chip e la cache. Questa tecnica è resa possibile dalla tecnologia 3DFabric di TSMC:

AMD 3D Chiplet Technology: A packaging breakthrough for high-performance computing.

— AMD (@AMD) June 1, 2021

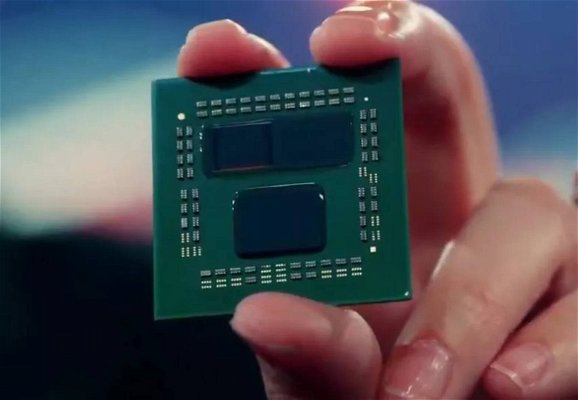

AMD ha assottigliato anche il die della cache 3D e aggiunto silicio strutturale al chip, ottenendo un processore che sembra identico dal punto di vista visivo a quello standard. Nel prototipo di Ryzen 9 5900X mostrato da Su è possibile vedere la SRAM ibrida 6x6 mm collegata alla parte superiore del chiplet. I dispositivi finali avranno 96MB di cache per CCD, per un totale di quasi 192MB su una CPU Ryzen 5000 a 12 o 16 core.

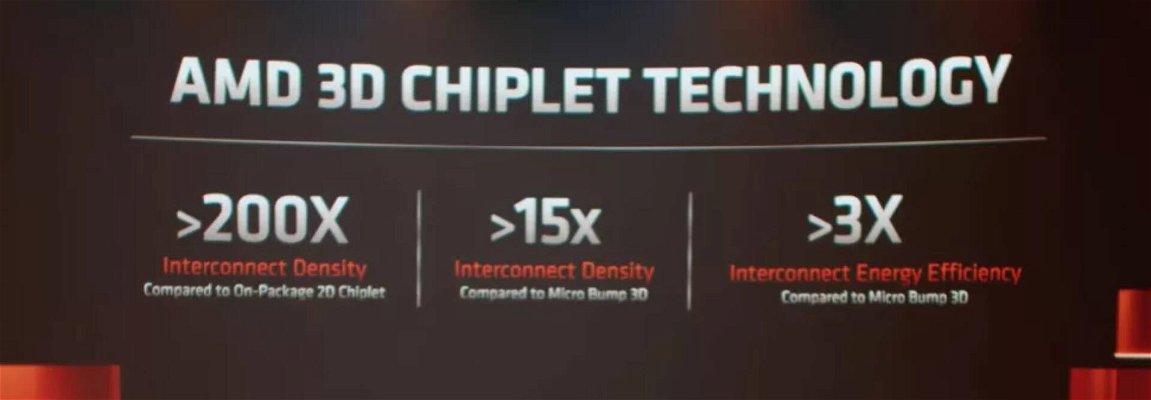

AMD ha utilizzato un approccio di bond ibrido con TSV che fornisce oltre 200 volte la densità di interconnessione dei chiplet 2D, con un miglioramento di 15 volte nella densità di interconnessione rispetto alle implementazioni 3D micro-bump e un miglioramento di tre volte nell'efficienza energetica dell'interconnessione.

Su ha affermato che questi progressi sono stati resi possibili dall’uso di un'interfaccia die-to-die senza microbump che utilizza un bond diretto rame-rame per migliorare la temperatura, la densità e il passo di interconnessione, oltre a produrre incredibili progressi dal punto di vista energetico. Su ha affermato che questa combinazione di caratteristiche ha reso questo approccio la tecnologia di stacking di silicio active-on-active più avanzata e flessibile al mondo.

Su ha messo a confronto il prototipo del Ryzen 9 5900X con la nuova 3D V-Cache contro un 5900X standard, con entrambi i chip bloccati a una velocità di clock di 4,0GHz, registrando prestazioni migliori del 12% su Gears 5, ma anche testando altri titoli, come Dota 2, Monster Hunter World, League of Legends e Fortnite, il guadagno medio è stato del 15%.

Alla ricerca di un nuovo PSU per alimentare la vostra prossima GPU? Corsair RM750X, alimentatore modulare da 750W, è disponibile su Amazon.