Arrivano nuovi rumor sull'atteso "Strix Halo" Zen 5, il chip che promette di portare le prestazioni dei giochi in mobilità ad un livello superiore, confrontandosi direttamente con i potenti processori M3 Max e M3 Pro di Apple montati nei modelli più recenti della linea MacBook Pro.

Il cuore dello "Strix Halo" sarebbe rappresentato da uno, o due, CCD "Zen 5", accompagnati da un grande die SoC che ospita una iGPU sovradimensionata e un controller di memoria LPDDR5X a 256 bit.

Questa configurazione consente di raggiungere prestazioni, sia grafiche che in termini di CPU, paragonabili ai recenti M3 Pro e M3 Max, mantenendo dimensioni PCB e alimentazione simili.

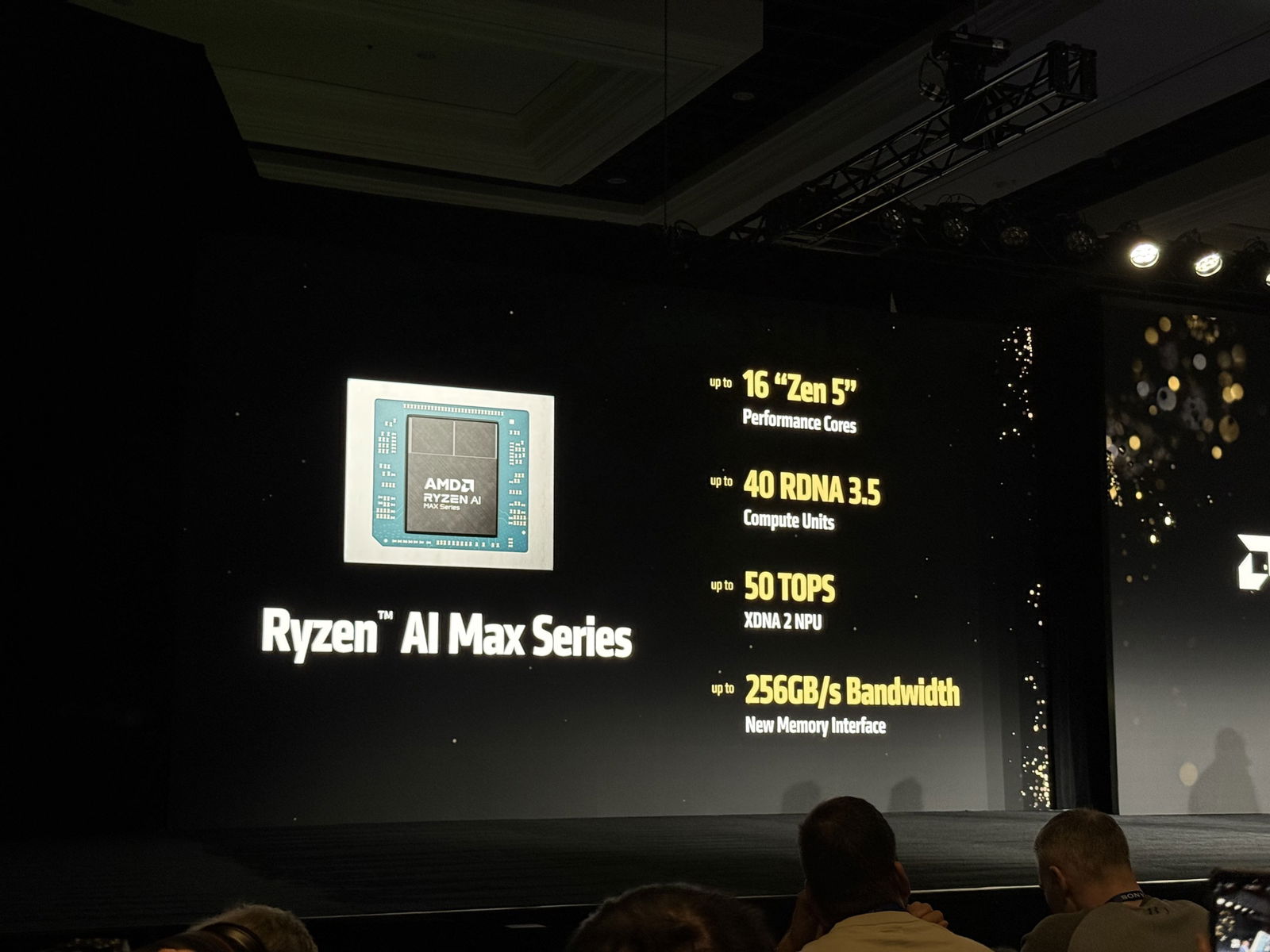

La iGPU, basata sull'architettura grafica RDNA 3+, vanta 40 unità di calcolo RDNA, che si traducono in 2.560 stream processor, 80 acceleratori AI, 40 acceleratori Ray e 160 TMU. La iGPU raggiunge un clock fino a 3,00 GHz, garantendo un'esperienza di gioco fluida e reattiva.

Per sostenere le esigenze della grafica, AMD ha implementato un'interfaccia di memoria LPDDR5X a 256 bit, offrendo una larghezza di banda della cache effettiva di circa 500 GB/s. Inoltre, i controller di memoria sono supportati da una cache L4 da 32 MB, che contribuisce a ottimizzare le prestazioni complessive del sistema.

Oltre alla potente iGPU, "Strix Halo" integra anche un NPU basato sull'architettura XDNA 2, con prestazioni stimabili intorno ai 45-50 AI TOPS. Tuttavia, l'I/O SoC del processore non è così completo come quello del "Fire Range", focalizzandosi maggiormente sull'utilizzo della iGPU. Dispone di PCIe Gen 5 con un totale di 12 lane, USB4 integrato da 40 Gbps e USB 3.2 Gen 2 da 20 Gbps.

Dal punto di vista delle prestazioni CPU, "Strix Halo" offre fino a 16 core "Zen 5", con una cache L3 di 32 MB per CCD o 64 MB di cache L3 totale. I CCD sono collegati al die SoC utilizzando IFOP convenzionale o Infinity Fanout links.

È importante, però, ricordarvi che al momento si tratta di indiscrezioni derivate da una presunta immagine reperita sul forum di ChipHell, dalla quale gli utenti si sono impegnati a creare alcune diapositive schematiche che, seppur molto plausibili, rimangono prive di conferma ufficiale da parte di AMD.