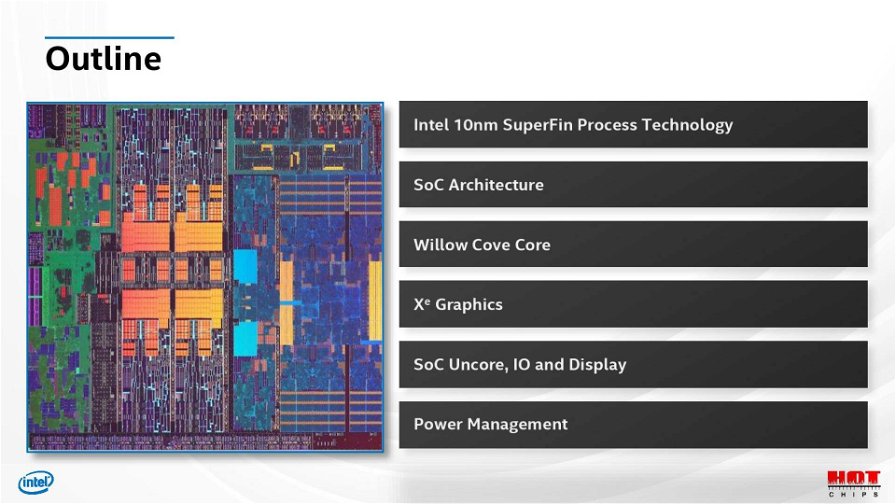

Intel ha iniziato a parlare approfonditamente di Tiger Lake la scorsa settimana in occasione del suo Architecture Day 2020, ma recentemente ha condiviso maggiori dettagli sui chip in arrivo all'Hot Chips 2020. Ciò include la prima immagine di un die quad-core Tiger Lake ed ulteriori informazioni sul suo migliorato bus di interconnessione tra i core.

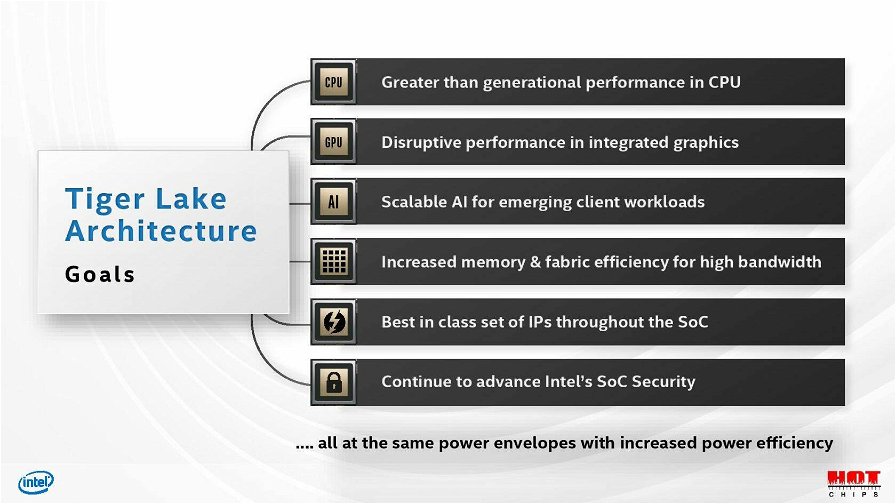

Ricordiamo che i processori Tiger Lake segnano il debutto dei transistor SuperFin da 10nm di Intel, iterazione migliorata dei 10nm già esistenti. Tra i vantaggi più importanti troviamo miglioramenti delle prestazioni di circa il 15-20% agli stessi valori di tensione/clock in alcune aree e frequenze di picco molto più elevate, probabilmente nell'intervallo di 5GHz per le componenti mobile.

Intel abbina questi transistor ottimizzati ai nuovi core Willow Cove, capacità di cache aumentata, ottimizzazioni per l'alta velocità, GPU Intel Xe LP (che offre fino al doppio delle prestazioni rispetto alle iGPU Intel di precedente generazione) e supporto per memorie fino a LPPDR5-5400 e PCI Express 4.0. Nel complesso, Intel afferma che Tiger Lake ha un livello di miglioramento delle prestazioni "superiore a quello generazionale".

Qui possiamo vedere l'immagine del die che Intel ha condiviso durante la sua presentazione a Hot Chips 2020. Intel non ha indicato specificamente i vari componenti presenti all’interno del die, ma la grande area blu nell'angolo in basso a destra è probabilmente l’unità grafica Xe LP (che comprende circa il 33% della matrice). Intel afferma che questo diagramma mostra un dispositivo a quattro core a scopo illustrativo, forse suggerendo che i modelli con un numero di core più elevato potrebbero arrivare in futuro.

Qui vediamo un'immagine del die *non ufficiale* dell’utente Twitter @Locuza_, specializzato nella decodifica di die complessi di processori. Ovviamente, dato che si tratta di un lavoro puramente teorico, potrebbero essere presenti alcuni errori.

Some quick annotations for the Tiger Lake die shot (Willow Cove CPU + Gen12/Xe LP graphics).

— Locuza (@Locuza_) August 17, 2020

It has several differences in comparison to Gen11 but on a high level Intel uses a similar floor plan.

*sorry for the repost but the white background I forgot to remove bothered me 😅* pic.twitter.com/zk53XCODQ0

Nella parte sinistra al centro del die vediamo quattro grandi cluster arancioni che sembrano essere le strutture della cache L1, L2 e L3, con il resto dei core che si estendono verso la parte superiore e inferiore. Più a sinistra, individuiamo il system agent e le interfacce I/O. Il ring agent al centro dell'immagine collega iGPU, cache/core e blocchi I/O di sistema. Intel ha portato Thunderbolt 4 in larga parte on-die sui processori Ice Lake originali, e possiamo vedere che la tradizione continua con l'ampia area del die dedicata in alto a destra del diagramma.

Intel ha confermato la maggiore capacità di cache per i suoi L2 (MLC) e L3 (LLC), che ora offrono rispettivamente 1,25MB e 12MB. La compagnia di Santa Clara ha utilizzato implementazioni di caching inclusivo per i suoi chip basati su Skylake, ma queste topologie richiedono che i dati conservati nella cache L2 privata vengano replicati nella cache L3 condivisa. Questa volta Intel ha aumentato la capacità L2, il che avrebbe portato a 5 MB di dati copiati da conservare nella cache L3. Pertanto, la società è passata ad uno schema non inclusivo che non richiede una copia dei dati L2 nella cache L3, lasciando così spazio a working set più grandi nella cache L3 condivisa.

Vediamo anche il supporto per la memoria LPPDRx-4267 sui primi modelli Tiger Lake e questo aumento del throughput aiuterà ad alimentare l’engine grafico Xe LP, decisamente affamato di larghezza di banda.

Intel è passata alla microarchitettura dual ring bus, anche se questa varia in modo significativo rispetto ai vecchi bus dual ring trovati su Skylake-X ad alto numero di core. In questo design, ogni stop serve entrambi gli anelli bidirezionali, il che significa che il bus dual ring di Willow Cove è essenzialmente costituito da due bus ring avvolti l'uno nell'altro in un solo controller. Questo approccio raddoppia la larghezza di banda, che di solito è il doppio di quella della memoria (172 GB/s in questo caso).

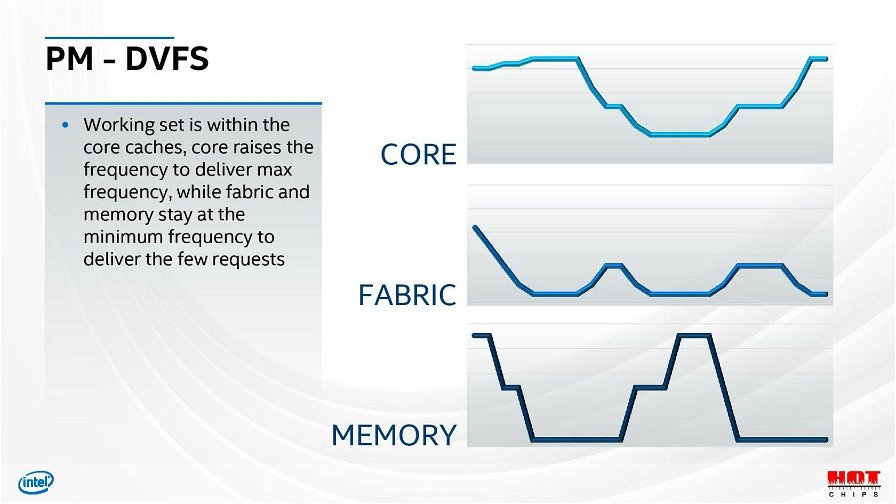

Mentre l'aumento del throughput tra i diversi elementi del processore, come i core e le interfacce I/O, promette prestazioni molto maggiori, questa scelta potrebbe anche portare ad un aumento del consumo energetico. La presentazione di Intel ha delineato molte delle tecniche utilizzate dall'azienda per ridurre i consumi garantendo comunque un tangibile aumento delle prestazioni, consentendo al SoC di allocare dinamicamente la potenza agli elementi che ne hanno bisogno per un dato carico di lavoro, migliorando così le prestazioni aggregate. Ad esempio, riducendo la larghezza di banda del fabric (e quindi la potenza) durante un carico di lavoro della CPU pesante a livello di elaborazione, il SoC può alimentare i core della CPU di maggiore potenza, aumentando così le prestazioni generali.

La CPU Intel Core i5-10600 con socket LGA1200 è in offerta su Amazon a circa 240 euro, un rapporto prestazioni prezzo davvero fantastico!