Nel contesto di una crescente domanda di chipset predisposti all'intelligenza artificiale (IA), TSMC, il produttore taiwanese leader dei semiconduttori, ha comunicato che la sua linea produttiva per il packaging avanzato è completamente prenotata i prossimi due anni. Questo fenomeno è largamente attribuibile alle esigenze di giganti tecnologici come Nvidia e AMD, che stanno spingendo i loro ordini al limite per soddisfare l'insaziabile appetito del mercato per le tecnologie AI più avanzate.

Il termine "packaging avanzato" si riferisce alle tecnologie e ai metodi utilizzati per incapsulare e proteggere i chip di silicio dopo la loro fabbricazione, oltre a collegarli a sistemi esterni come schede di circuito. Questo processo è cruciale perché protegge i chip sensibili e garantisce la connessione affidabile tra il silicio e il resto del dispositivo elettronico.

L'Economic Daily News riferisce che gran parte della domanda proviene dalle principali aziende di servizi cloud. Questa situazione è stata ulteriormente confermata dalle dichiarazioni di C.C. Wei, a capo di TSMC, nel corso di una recente call sugli utili aziendali.

TSMC sta rispondendo a questa domanda espandendo attivamente la propria capacità di packaging avanzato. Wendell Huang, CFO dell'azienda, ha parlato di "piani di espansione dell'impronta produttiva globale" per far fronte alla crescente richiesta del mercato.

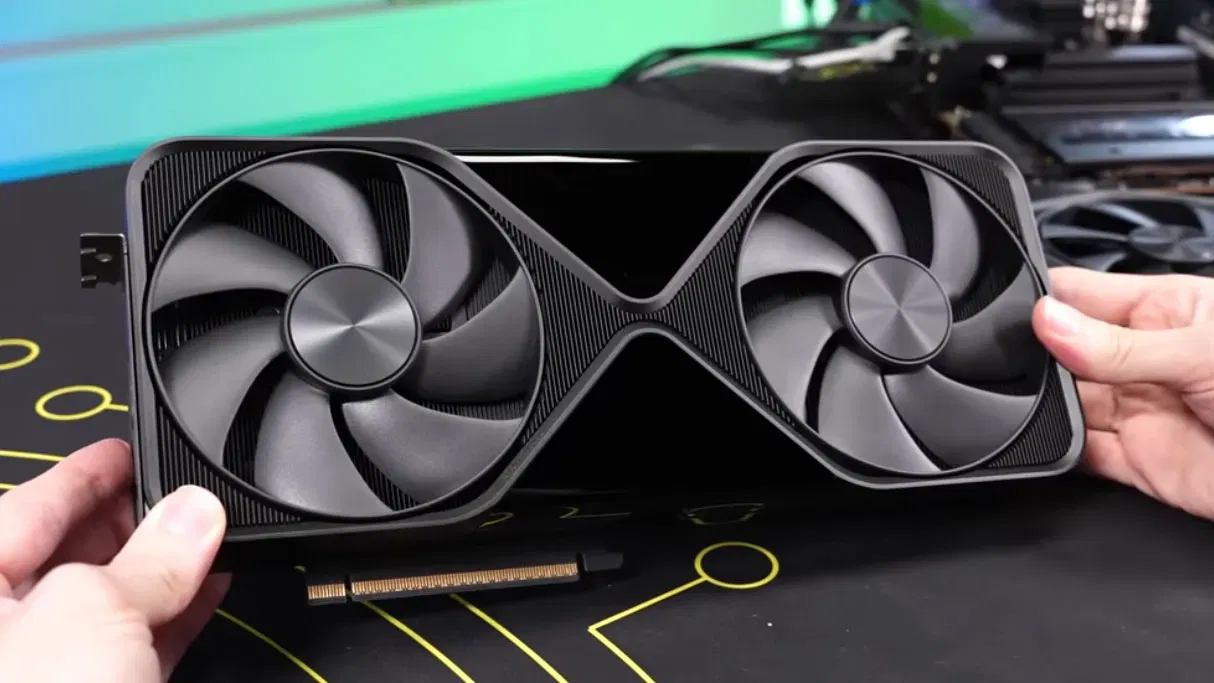

Sia Nvidia che AMD si affidano ai processi sofisticati di TSMC per i loro chip di punta destinati all'IA. Nvidia utilizza il processo a 4nm e il confezionamento avanzato Chip-on-Wafer-on-Substrate (CoWoS) per i suoi chip H100, mentre AMD impiega i processi a 5 e 6nm per gli acceleratori AI della serie MI200. Inoltre, AMD sfrutta il packaging avanzato System-on-Integrated-Chips (SoIC) per integrare die di CPU e GPU, oltre al CoWoS per i prodotti di memoria ad alta larghezza di banda (HBM).

Si prevede che entro la fine dell'anno, TSMC riuscirà a produrre CoWoS a un tasso mensile compreso tra 45.000 e 50.000 unità, mentre la produzione di SoIC dovrebbe raggiungere le 5.000 e 6.000 unità al mese nello stesso periodo.

Tuttavia, la domanda di packaging avanzato sta mettendo in luce le criticità nella gestione delle capacità produttive del colosso taiwanese. Durante una recente call sugli utili, si è discusso di come TSMC intenda distribuire queste risorse limitate tra i diversi clienti, con un particolare riferimento alla necessità di bilanciare le esigenze dei grandi clienti con il sostegno ai partner più piccoli o strategici.

Jeff Su, direttore delle relazioni con gli investitori di TSMC, ha affermato che l'azienda sta facendo del suo meglio per aumentare significativamente la capacità, che quest'anno sarà più che raddoppiata rispetto all'anno scorso, ma resta comunque insufficiente per soddisfare la domanda completa del mercato.

Come se non bastasse, TSMC ha dovuto affrontare ulteriori problemi in seguito al recente terremoto che ha colpito l'impianto produttivo di CoWoS causando ingenti danni. Nonostante ciò, l'azienda ha assicurato che l'offerta di chip non ne ha risentito, sebbene possa influire sui futuri investimenti in capitale. Inoltre, l'industria della memoria ha registrato un insperato aumento dei prezzi di DRAM e NAND flash a seguito dell'evento sismico, con previsioni di ulteriori incrementi nei prossimi mesi.