I ricercatori della Purdue University hanno raggiunto un importante risultato per ciò che riguarda la progettazione dei transistor di prossima generazione, che potrebbe consentire un'estensione della vita dei semiconduttori a base di silicio. Il nuovo design, intitolato CasFET (Cascade Field Effect Transistor) è un ulteriore passo avanti sulla strada della miniaturizzazione, in quanto consente di utilizzare tensioni di commutazione inferiori e avere un consumo energetico più basso. Tillman Kubis, Research Assistant Professor del dipartimento Electrical and Computer Engineering, ha affermato che questa ricerca cerca di affrontare le maggiori difficoltà nella miniaturizzazione dei transistor.

"Essi [i transistor] hanno bisogno di una corrente ON sufficientemente alta e di una corrente OFF abbastanza bassa, con una piccola differenza per passare da una all'altra" - ha detto Kubis - "Queste sfide hanno rallentato significativamente il downscaling dei transistor negli ultimi otto anni, rendendo sempre più difficile l'introduzione di generazioni di CPU più potenti". Uno dei casi più noti inerenti a questo problema è stata la transizione di Intel ai processi a 10nm e 7nm, che ha portato a una serie di ritardi che hanno aiutato la “rinascita” del diretto concorrente AMD nel mercato delle CPU.

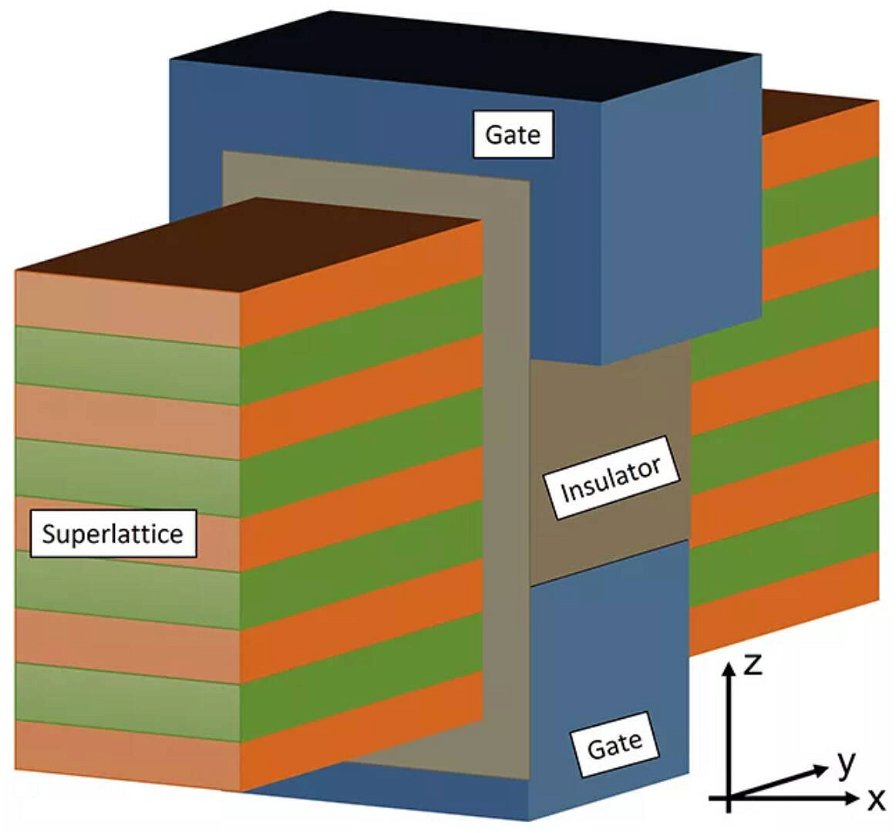

Samsung sta impiegando la tecnologia GAAFET (Gate All Around Field Effect Transistor) per il processo a 3nm, con una produzione di massa prevista per quest'anno. La tecnologia, che segue FinFet, ridisegna i transistor per presentare quattro porte su tutti e quattro i lati di un canale. Ciò fornisce un migliore isolamento dai transistor vicini, limita le perdite di tensione e consente di applicare voltaggi inferiori per lo stesso effetto di commutazione. Ciò a sua volta permette di distribuire un maggior numero di transistor più ravvicinati, aumentando la densità. Samsung afferma che questo approccio consente una riduzione delle dimensioni del 35% (rispetto al FinFET a 5nm). Lo sviluppo di CasFET rappresenta un possibile passo successivo nella produzione di transistor, offrendo strutture superlattice che sono perpendicolari alla direzione di trasporto del transistor, consentendo stati a cascata commutabili. Questo in realtà impiega effetti appresi dai laser a cascata quantica ed essenzialmente permette un controllo della tensione più preciso.

Il team sta attualmente sviluppando il primo prototipo CasFET ed è ancora in fase di progettazione per la struttura e i materiali complessivi, cercando di trovare il giusto equilibrio tra costo, disponibilità del materiale, facilità di transizione dalla tipica produzione di transistor e prestazioni. Per ora, il prototipo non offre il profilo prestazionale che stanno cercando. Tuttavia, il lavoro è abbastanza promettente, tanto che Purdue ha richiesto la protezione del brevetto presso l'U.S. Patent and Trademark Office.