AMD ha recentemente depositato un brevetto per una nuova architettura di CPU che comprende dei core ad alte prestazioni ed altri a consumo energetico ridotto con un metodo per velocizzare la comunicazione tra le due unità.

Il tipo di architettura big.LITTLE di AMD è stata scovata in una richiesta di brevetto dall'utente Twitter @Underfox3 che ne ha condiviso i dettagli. Nel brevetto viene dettagliato un metodo di comunicazione dei thread tra core ad alte prestazioni e altri a maggiore efficienza energetica. Questo non assicura che AMD voglia portare sul mercato questo tipo di soluzione, tuttavia conferma l'impegno dell'azienda nella ricerca di soluzioni innovative nel campo delle architetture ibride.

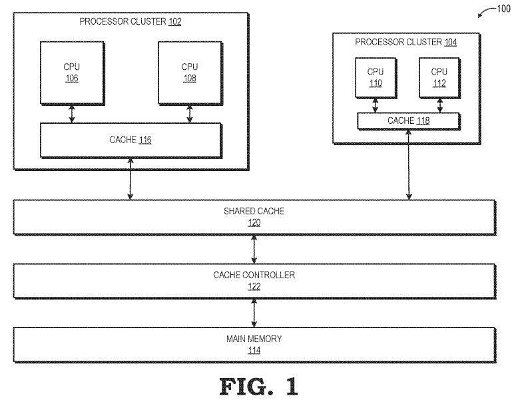

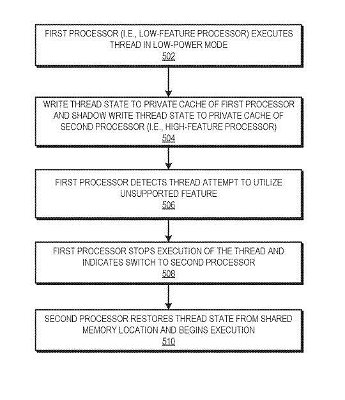

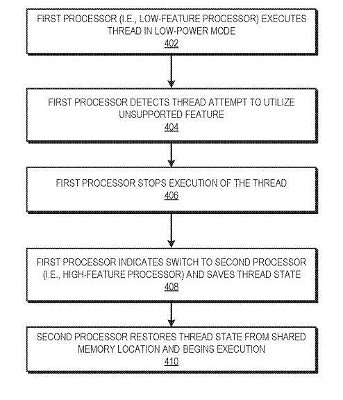

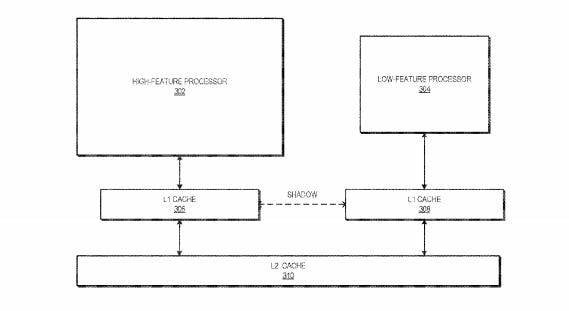

Il brevetto di AMD descrive un'implementazione che consente l'esecuzione di un sottoinsieme di istruzioni su core di elaborazione più grandi e completi ottimizzati per prestazioni più elevate, mentre un secondo sottoinsieme di istruzioni su core più piccoli e semplificati progettati per l'efficienza energetica. Viene descritto un metodo che consente ai core di utilizzare una posizione di memoria condivisa per velocizzare il trasferimento dei thread, in base a determinate variabili, tra i due tipi di core. Quando un core non è occupato può essere spento, migliorando così ulteriormente il consumo di energia.

Non è la prima volta che si parla di questo tipo di architettura, molto diffusa nell'ambito smartphone e già in lavorazione anche da parte di Intel con i suoi chip Lakefield. Per sfruttare al massimo l'efficienza di queste soluzioni, tuttavia, è necessario che il sistema operativo sia in grado di trattare questo tipo di architettura. Il metodo descritto da AMD sembrerebbe permettere direttamente ai core di decidere indipendentemente come suddividersi il carico di lavoro. Ad esempio, se i core più prestanti sono sottoutilizzati, il processore sposterebbe il thread sui core meno potenti. Allo stesso modo, se i core meno potenti risultano sovrautilizzati, il thread verrebbe spostato su quelli più potenti.

Questo approccio potrebbe ridurre o addirittura eliminare la necessità che sia l'OS a dover prendere in carico questo tipo di operazioni, semplificandone lo sviluppo e migliorandone l'efficienza. Underfox avverte che il brevetto è ancora in fase di aggiustamento, quindi potrebbe essere soggetto a modifiche.

In attesa dell'arrivo delle nuove APU per desktop, il Ryzen 5 3400G con GPU Vega 11 rimane ancora un ottimo affare al prezzo di circa 160 euro su Amazon.