Lo scorso aprile Samsung Electronics annunciò l'intenzione di investire 120 miliardi di dollari entro il 2030 nel business nei chip, al fine di diventare la potenza numero uno nella produzione di semiconduttori. Per farlo, a fronte della fortissima concorrenza di TSMC, non ha altra soluzione che accelerare il passo.

Già in tempi non sospetti Samsung delineò una roadmap di processi produttivi molto aggressiva e, stando alle ultime notizie, sembra che sia anche a buon punto per trasformarla in prodotti concreti. Parlando infatti alla stampa sudcoreana (Maeil Economy), l'azienda ha annunciato di aver già realizzato soluzioni sperimentali con processo produttivo a 3 nanometri.

Per ora si tratta di prototipi, non sappiamo di che genere, ma visto che l'obiettivo è avviare la produzione in volumi a 3 nanometri nel corso del prossimo anno, sembra che tutto stia procedendo secondo i piani.

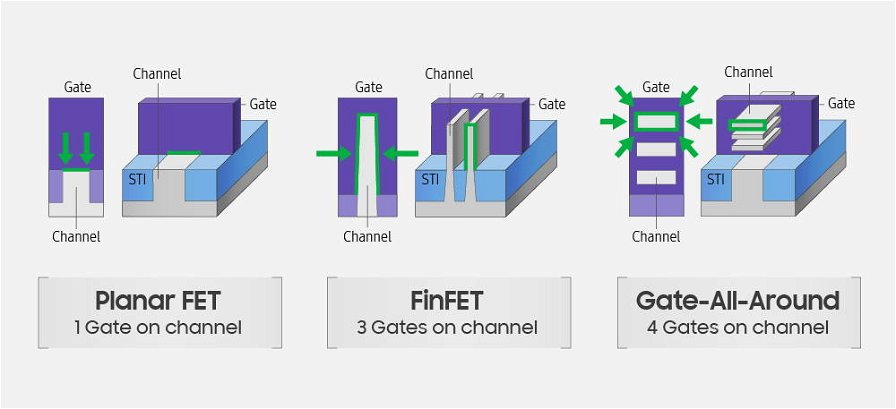

Come già spiegato nei dettagli in questo articolo, Samsung si sta preparando al momento in cui i transistor FinFET non potranno più scalare (sono stati introdotti da Intel nel 2012 con le CPU Ivy Bridge a 22 nanometri tramite i cosiddetti transistor tri-gate). Per farlo l'area di contatto tra canale e gate dovrà essere aumentata, e la risposta in tal senso prende il nome "Gate All Around" (GAA).

GAA interviene sulle dimensioni del transistor per assicurare che il gate sia anche sotto il canale, non solo sopra e ai lati. Questo permette al design GAA di impilare i transistor verticalmente anziché lateralmente. I FET basati su GAA (GAAFET appunto) possono avere diversi form factor e tra le diverse opzioni l'azienda ha pensato di rendere il canale come un foglio orizzontale, incrementandone il volume e ottenendo così vantaggi in termini di prestazioni e scaling.

Questo design è quello che l'azienda definisce Multi-Bridge Channel FET, o MBCFET. Il progetto - in sviluppo dal 2002 - è estremamente personalizzabile, ossia l'ampiezza del nanofoglio (nanosheet) va a influire direttamente su consumi e prestazioni: maggiore è l'ampiezza, migliori sono le prestazioni.

Con il processo a 3 nanometri, Samsung punta a offrire una riduzione del 35% della dimensione dei die rispetto al proprio processo a 5 nanometri FinFET, abbassando il consumo di ben il 50%. Oppure, qualora il consumo rimanesse identico, i 3 nanometri saranno in grado di garantire un incremento prestazionale di circa il 30%.