Durante l'IEEE International Symposium on High-Performance Computer Architecture che si terrà a febbraio, ricercatori della University of Illinois Urbana-Champaign e della University of California Los Angeles presenteranno quello che dipingono come un megaprocessore formato da oltre 40 GPU poste tutte su un wafer di silicio.

Qualcosa che ricorda quanto tentò di fare Trilogy Systems negli anni '80, puntando sulla tecnica wafer scale integration (WSI) con l'obiettivo di creare un megachip da 2,5 pollici su un lato (maggiori dettagli su Wikipedia inglese).

Secondo le simulazioni fatte sinora, il "mostro" messo a punto dai ricercatori statunitensi può accelerare i calcoli di quasi 19 volte, riducendo la combinazione di consumo energetico e ritardo del segnale di oltre 140 volte, rispetto alle soluzioni odierne. Il tutto è spiegato su IEEE Spectrum. Vale la pena di precisare che non stiamo parlando di un progetto rivolto ai computer desktop, bensì che in prospettiva guarda a supercomputer e datacenter di grandi dimensioni.

"Il grande problema che stiamo provando a risolvere è l'overhead della comunicazione tra unità di calcolo", ha spiegato il professore Rakesh Kumar. "I supercomputer suddividono le applicazioni su centinaia di GPU poste in circuiti stampati differenti e che comunicano su interconnessioni a lungo raggio. Questi collegamenti assorbono energia e sono lenti rispetto alle interconnessioni interne ai chip stessi. Inoltre, a causa delle disparità nelle proprietà meccaniche dei chip e dei circuiti stampati, i processori devono essere inseriti in package che limitano severamente il numero di input e output che un chip può usare. Perciò portare i dati da una GPU all'altra comporta un'incredibile quantità di overhead".

Quello a cui aspirano i ricercatori sono connessioni tra le GPU veloci, efficienti e abbondanti come le interconnessioni nei chip. Connessioni così veloci potrebbero far funzionare le 40 GPU come un'unica grande GPU. Secondo Kumar da una prospettiva di un programmatore "tutto apparirebbe come se fosse sulla stessa GPU".

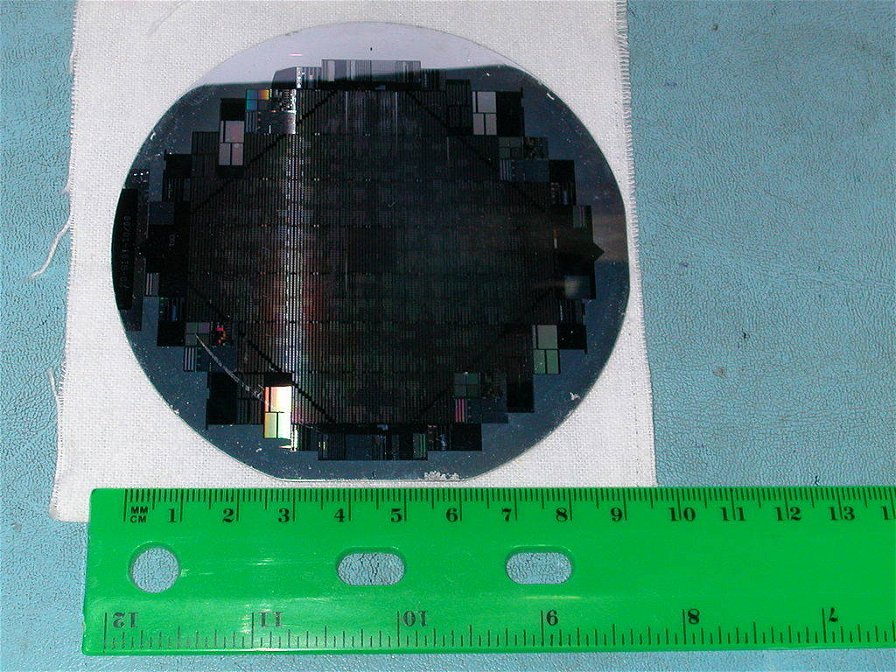

Una soluzione sarebbe quella di usare tecniche di produzione standard per realizzare tutte e 40 le GPU sullo stesso wafer e aggiungere le interconnessioni. Le possibilità che durante la produzione emerga un difetto fatale però non solo sono alte, ma aumentano con la dimensione del chip.

Perciò ha più senso partire con GPU di dimensioni normali che hanno già superato test di qualità e trovare una tecnologia connetterle al meglio. Il team crede di aver trovato la soluzione nella tecnologia silicon interconnect fabric (SiIF). SiIF sostituisce il circuito stampato con il silicio, quindi non vi è alcuna discrepanza meccanica tra il chip e il circuito stampato e perciò non è necessario un package.

Il wafer SiIF è realizzato con uno o più strati di interconnessioni di rame da 2 micrometri spaziate tra loro di 4 micrometri. Valori comparabili al livello superiore delle interconnessioni su un chip. Nei punti in cui le GPU sono destinate a collegarsi, il wafer di silicio ha delle colonne di rame corte distanziate di circa 5 micrometri. La GPU viene allineata sopra di queste, schiacciata verso il basso e riscaldata. Questo processo consolidato, chiamato thermal compression bonding (incollaggio a compressione termica), fa sì che i pilastri in rame si fondano con le interconnessioni in rame della GPU. La combinazione di interconnessioni strette e spaziatura ridotta consente di avere almeno 25 volte più input e output su un chip, secondo i ricercatori dell'Illinois e dell'UCLA.

Kumar e i suoi collaboratori hanno dovuto prendere in considerazione una serie di limitazioni nella progettazione della GPU in "scala wafer", compresa la quantità di calore rimovibile, il modo in cui far comunicare le GPU più rapidamente tra loro e come fornire energia sull'intero wafer.

Quest'ultimo punto si è rivelato uno dei limiti maggiori. Con un'alimentazione standard di 1 volt, le interconnessioni sul water SiIF consumerebbero 2 kilowatt. Il team di Kumar ha così portato la tensione a 48 volt, riducendo la quantità di corrente necessaria e perciò la perdita di energia. Questa soluzione richiede di diffondere i regolatori di tensione e i condensatori di condizionamento del segnale sul wafer, occupando spazio utile a mettere più moduli GPU. Ciononostante, in un design i ricercatori sono stati in grado di inserire 41 GPU.

In una simulazione di questo progetto hanno riscontrato che ha il potenziale per accelerare sia il calcolo sia il movimento dei dati consumando meno energia rispetto a quanto farebbero 40 GPU server standard. Al momento non sono chiari aspetti come il raffreddamento richiesto, ma il professore Kumar ha dichiarato che il lavoro per arrivare a un prototipo è partito.