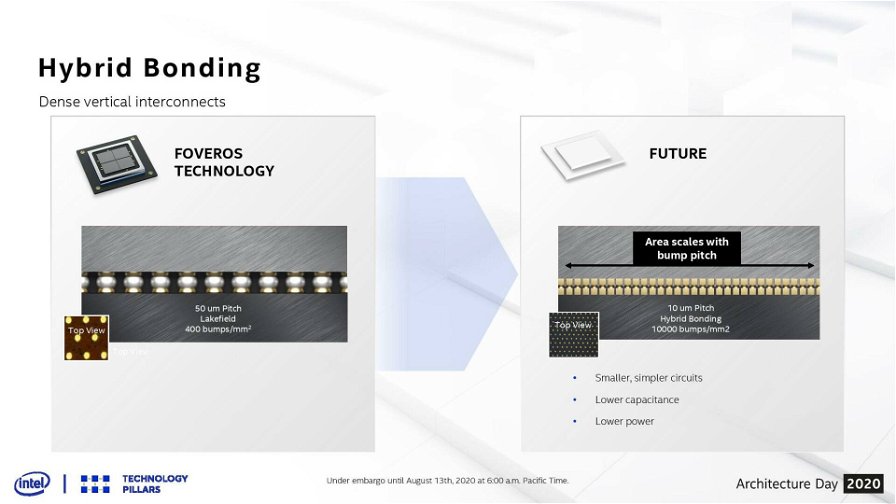

Nel corso del recente Architecture Day 2020, Intel ha presentato i suoi progetti inerenti alle prossime tecnologie che impiegherà per il packaging e lo stacking dei chip, le quali consentiranno di aumentare il numero di connessioni tra le varie parti dei processori, massimizzando in questa maniera la banda passante e riducendo la latenza, anche tra strati che sono stati realizzati con processi produttivi diversi.

La compagnia di Santa Clara ha ideato la propria topologia di interconnessione fisica, Embedded Multi-Die Interconnetto Bridge (EMIB), che permette un’espansione 2D e stacking Foveros 3D die-to-die per l’espansione verticale. Tuttavia, questo sistema verrà soppiantato in futuro da "Hybrid Bonding”, che Intel sfrutterà per aumentare il numero di densità dei bump di un fattore pari a 3-10 rispetto alle tecnologie precedenti. I primi chip di prova hanno usato questo approccio con la SRAM, arrivando a 10.000 bump per mm², con una potenza necessaria inferiore a 0.05 picojoules per bit. Stando ad Intel, questo permetterà di realizzare circuiti più piccoli e semplici con consumi inferiori ed una efficienza sensibilmente aumentata.

Tutte queste tecnologie saranno utlizzate anche per gestire al meglio le temperature e, stando all’azienda, sarà necessario progettare insieme tutti i vari strati, e non in modo indipendente, per accoppiare in maniera perfetta le loro caratteristiche elettriche e termiche, a tutto vantaggio dell'assorbimento energetico e dell' affidabilità.

Con l’avanzamento tecnologico sarà sempre più necessario equilibrare al meglio potenza, capacità di elaborazione, dimensioni e temperature. Tuttavia, prima di vedere all’opera pienamente questo nuovo approccio dovremo attendere ancora un po’. Ad esempio, Ramune Nagisetty di Intel ha affermato che Foveros è stato brevettato nel 2008, ma c’è voluto quasi un decennio prima che il processo diventasse fisicamente fattibile su larga scala e con un rendimento sufficientemente alto da consentire ad un prodotto di essere commercializzato.

Qualche giorno fa vi abbiamo anche parlato più nel dettaglio dei processori Tiger Lake, i quali puntano a dominare la fascia di mercato delle CPU a basso consumo da 7W a 15W nel 2020, con nuovi chip della famiglia “H” con potenze variabili tra 25W e 45W in arrivo nel 2021. I SoC sono realizzati con il nuovo processo produttivo a 10nm SuperFin della casa americana che ne consente un aumento di efficienza a due cifre rispetto ai modelli a 10nm classici.

Il portatile HP Pavillion 15 con AMD Ryzen 5 3500U, 8GB di RAM, 256GB di SSD e GPU AMD Radeon Vega 8 è attualmente in vendita a prezzo scontato su Amazon.