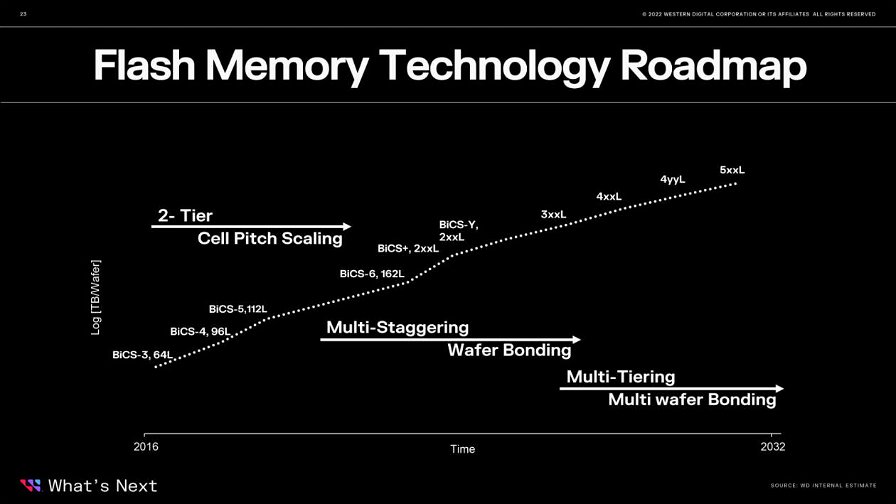

Western Digital (WD) ha presentato questa settimana la roadmap inerente ai suoi chip BiCS 3D NAND. L'azienda, in collaborazione con Kioxia, intende continuare a sviluppare questa tecnologia, introducendo, nel tempo, miglioramenti sia a livello di capacità che di velocità.

La sesta generazione di memorie BiCS sarà caratterizzata da 162 strati attivi e sarà impiegata per 3D NAND QLC da 1Tb con una dimensione del die di 68mm². Dovrebbe anche offrire maggiori prestazioni in ambito I/O, che andranno a sfruttare meglio l'interfaccia PCI Express 5.0. Nonostante siano già stati annunciati chip a 176 strati da altri produttori, la proposta di WD si differenzia per le ridotte dimensioni delle celle di memoria, che dovrebbe rendere i dispositivi più facili ed economici da produrre. La produzione di massa delle memorie in configurazioni QLC e TLC inizierà alla fine del 2022 (corrispondente al secondo trimestre dell'anno fiscale 2023).

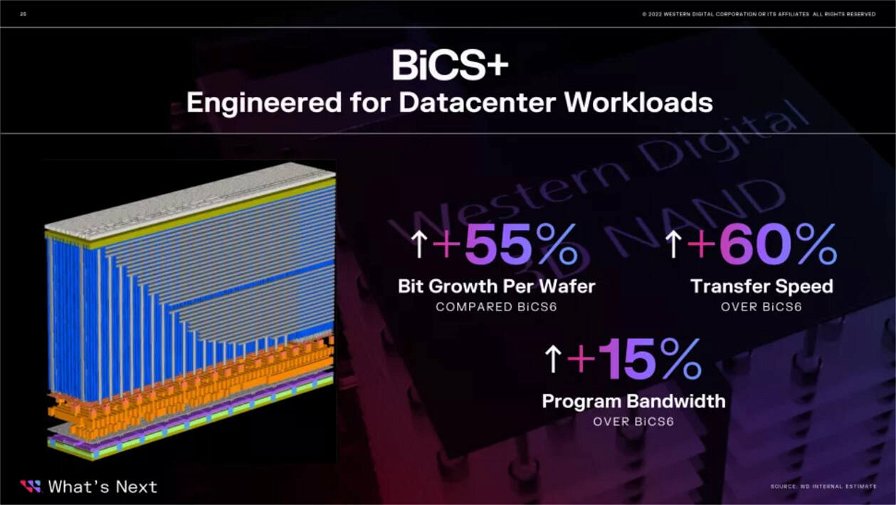

Oltre a ciò, per gli utilizzi tipici dei data center, l'azienda sta già preparando le memorie BiCS+, che rispetto alle BiCS di sesta generazione avranno un aumento di bit per wafer del 55% grazie all'impiego di 200 strati e una velocità di trasferimento superiore sino al 60%. Nonostante non siano state fornite informazioni più precise, le memorie BiCS+ dovrebbero consentire alla società di produrre SSD per data center ad alta capacità con form factor standard. Il debutto sul mercato è previsto per il 2024.

Ancora più avanti, WD realizzerà memorie 3D NAND con oltre 500 strati impiegando tecniche avanzate, ma per vederle all'opera dovremo attendere almeno fino al 2030, come affermato da Siva Sivaram, presidente della divisione "technology and strategy" di Western Digital:

Si può vedere [che] nei prossimi 10+ anni abbiamo una buona tabella di marcia che prevede lo sviluppo e l'impiego di nuove tecnologie per arrivare fino a più di 500 strati. Abbiamo iniziato con la 3D NAND a due livelli a scalare il passo delle celle e probabilmente introdurremo il wafer bonding, faremo il multi tearing, il multi wafer bonding. Queste tecnologie sono già in fase di lavorazione per poterle introdurre nel nodo giusto [...].