TSMC ha annunciato che avvierà la produzione commerciale di chip usando la seconda generazione del processo produttivo a 7 nanometri, nota come N7+, nel terzo trimestre di quest’anno. La tecnologia N7+ è la prima ad adottare la litografia EUV (Extreme Ultra Violet) e sarà alla base di numerosi prodotti AMD di prossima generazione (EPYC Milan, Ryzen 4000) - ma non solo.

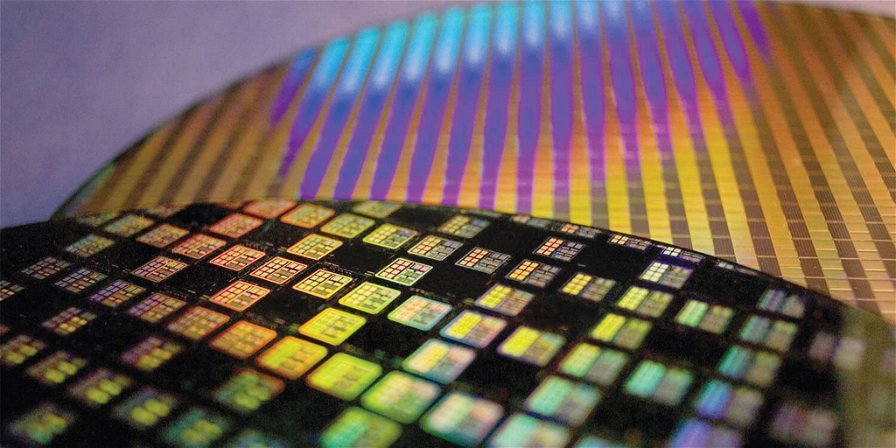

Secondo indiscrezioni il nuovo processo prevede l’uso della litografia EUV per quattro layer non critici. La litografia, lo ricordiamo, è il processo di riproduzione di un pattern complesso su un wafer partendo da una maschera. Il wafer è ricoperto con un polimero fotosensibile che viene inciso al fine di creare i componenti. EUV, ultravioletto estremo, è la porzione di spettro usata per l’incisione sul polimero che ricopre il wafer.

La fonderia taiwanese ha affermato che le rese della seconda generazione sono migliorate e ora hanno raggiunto un livello pari a quello della prima (N7). Quest’anno, di conseguenza, la produzione a 7 nanometri aumenterà drasticamente, anche se già sul finire dello scorso anno aveva registrato un’importante partenza.

TSMC prevede che la sua capacità produttiva totale raggiungerà l’equivalente di 12 milioni di wafer da 12 pollici nel 2019, con la produzione a 7 nanometri che farà segnare un +150% toccano 1 milione di unità.

Kevin Zhang, VP of business development, ha inoltre affermato che TSMC sta seguendo i piani per avviare la produzione in volumi di chip a 5 nanometri nel primo trimestre 2020. TSMC adotterà la litografia EUV in modo più esteso per i 5 nanometri e ha già avviato la fase di risk production, come riportato in precedenza.

TSMC ha inoltre iniziato l’installazione dei macchinari produttivi nella Fab 18 situata presso il Southern Taiwan Science Park (STSP). L’impianto sarà preposto proprio alla produzione di chip a 5 nanometri prevista per il 2020. L’azienda taiwanese ha inoltre riservato uno spazio adiacente alla Fab 18 per realizzare un impianto che si occuperà di produrre con processo produttivo a 3 nanometri.

.png)